# QATAR UNIVERSITY

## COLLEGE OF ENGINEERING

# MODULAR MULTILEVEL CONVERTER-BASED HVDC TRANSMISSION

## SYSTEMS

BY

# NADA AHMED HUSSEIN

A Thesis Submitted to

the Faculty of the College of

Engineering

in Partial Fulfillment

of the Requirements

for the Degree of

Masters of Science in Electrical Engineering

[June] 2018

© 2018 Nada Hussein . All Rights Reserved.

# COMMITTEE PAGE

The members of the Committee approve the Thesis of [Nada Hussein ] defended on 23/05/2018.

[Ahmed Massoud] Thesis/Dissertation Supervisor

> [Lazhar Ben Ibrahim] Committee Member

[Haitham Abu Rub] Committee Member

[Nader Meskin] Committee Member

Approved:

Khalifa Al-Khalifa, Dean, College of Engineering

### ABSTRACT

#### HUSSEIN, NADA., Masters : June : [2018],

Masters of Science in Electrical Engineering

# Title: MODULAR MULTILEVEL CONVERTER-BASED HVDC TRANSMISSION

### **SYSTEMS**

Supervisor of Thesis: Ahmed. Massoud.

High-Voltage Direct Current (HVDC) transmission systems based on Voltage Source Converter (VSC) technology has attracted significant interest recently for transmitting large amounts of power over long distances using back-to-back or point-to-point configurations. VSC-HVDC has been addressed for various HV applications such as DC interconnections, Multi-Terminal HVDC Transmission (MT-HVDC), installation of offshore wind power generation such as Europe super DC grid and installation of other renewable energy sources. Several classes of VSC topologies can be employed in HVDC systems including the conventional two and three-level converters, multilevel converters, and Modular Multilevel Converters (MMCs) that has been recently introduced and investigated for HVDC applications. MMC is penetrating the modern HVDC transmission market, due to its inherent features such as scalability, modularity, and fault ride through capability. Therefore, this thesis investigates and models a point-to-point VSC-based HVDC transmission system using nine-level MMC transient model, and 25-level MMC averaged model using MATLAB/Simulink platform to meet the requirements of HVDC systems such as HV requirements and fault ride through capability. However, a point-topoint HVDC system using conventional two-level converter is modeled and simulated using MATLAB/Simulink as a starting and benchmarking model. MMC transient model employed in this study is based on Half-Bridge Sub-Modules (HB-SMs) due to its simple structure, yet, other structures are discussed. Nevertheless, balancing of the floating capacitors is one of the challenges associated with MMCs. Therefore, capacitor voltage balancing and its modeling is addressed. Then the average model of the MMC-based HVDC system is investigated. Moreover, the behavior during DC side faults is investigated, and the employment of hybrid DC circuit breakers and Hybrid Current Limiting Circuit (HCLC) are introduced for protection and limiting the DC fault current. This introduces a platform for studying large MMC-based HVDC systems in normal operation and during faults.

DEDICATION

This work is dedicated to my family for their continuous support.

## ACKNOWLEDGMENTS

My sincere gratitude goes to my family and friends for their continuous support throughout my Master degree studies, especially their encouragement during my thesis work. Special thanks to my thesis supervisor Dr. Ahmed Massoud for his patience, guidance, support, encouragement, and for being always there for help. Many thanks to the Department of Electrical Engineering, faculty, and staff, for their support and encouragement. It has been a pleasure being a part of the department.

I would like to extend my gratitude to Qatar General Electricity and Water Corporation employees for their support and encouragement during my thesis work.

# TABLE OF CONTENTS

| DEDICATIONv                                               |  |  |

|-----------------------------------------------------------|--|--|

| CKNOWLEDGMENTS vi                                         |  |  |

| IST OF ABBREVIATIONS xi                                   |  |  |

| LIST OF TABLES xiv                                        |  |  |

| JIST OF FIGURESxv                                         |  |  |

| CHAPTER 1: INTRODUCTION1                                  |  |  |

| .1. Background1                                           |  |  |

| .2. Thesis Objective                                      |  |  |

| .3. Thesis Outline                                        |  |  |

| CHAPTER 2: VSC-BASED HVDC SYSTEMS7                        |  |  |

| .1 VSC-HVDC Systems                                       |  |  |

| Applications of VSC-HVDC systems                          |  |  |

| 1.2. VSC-HVDC system structure                            |  |  |

| .2. Two-Level Inverter HVDC system                        |  |  |

| .3. MMC-Based HVAC15                                      |  |  |

| <i>.3.1. MMC</i>                                          |  |  |

| <i>.3.2. MMC during fault at DC side</i>                  |  |  |

| .4. Conclusion21                                          |  |  |

| CHAPTER 3: TWO-TERMINAL TWO-LEVEL VSC-BASED HVDC SYSTEM23 |  |  |

| 3.1.   | System overview                                           |

|--------|-----------------------------------------------------------|

| 3.2.   | Control of Two-terminal two-level VSC-based HVDC system25 |

| 3.2.1. | Control of Sending Terminal Converter26                   |

| 3.2.2. | Control Of Receiving Terminal Converter29                 |

| 3.2.3. | Simulation Results                                        |

| 3.3.   | DC Side Fault                                             |

| 3.4.   | HVDC Systems Protection                                   |

| 3.4.1. | Case 1: Low resistance Fault42                            |

| 3.4.2. | Case 2: High Resistance Fault45                           |

| 3.4.3. | Implementation of DCCB48                                  |

| 3.5.   | Conclusion                                                |

| CHAPT  | ER 4: TWO-TERMINAL MMC-BASED HVDC SYSTEM54                |

| 4.1.   | Modular Multilevel Converter (MMC)                        |

| 4.1.1. | MMC topology and operation54                              |

| 4.1.2. | MMC Mathematical Model55                                  |

| 4.1.3. | Modulation Technique                                      |

| 4.2.   | Capacitor Voltage Balancing                               |

| 4.2.1. | The applied Voltage Balancing Technique61                 |

| 4.2.2. | Capacitor Voltage Balanceng Simulation Results62          |

| 4.3.   | Two-terminal MMC-Based HVDC System                        |

|        | viii                                                      |

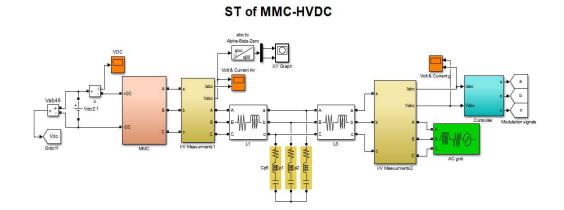

| 4.3.1. | MMC-HVDC Simulation Results70                       |

|--------|-----------------------------------------------------|

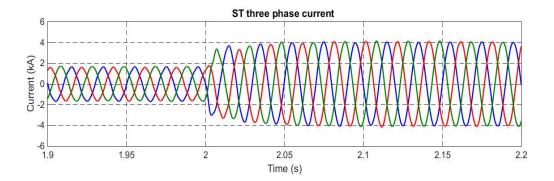

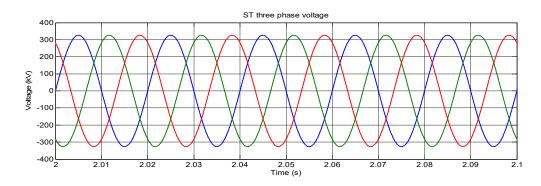

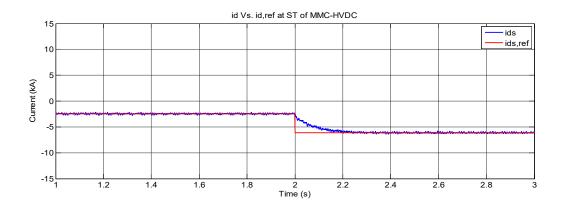

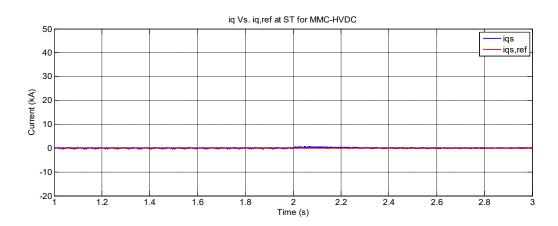

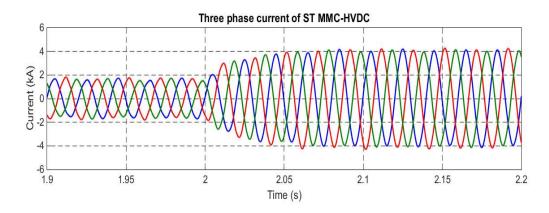

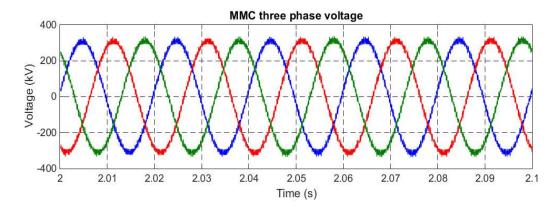

| 4.3.2. | ST Simulation Results71                             |

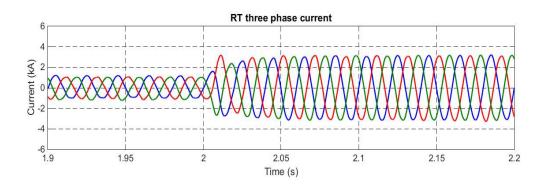

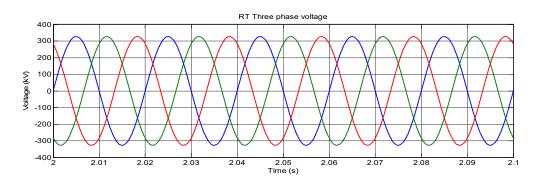

| 4.3.3. | RT Simulation Results75                             |

| 4.4.   | DC Side Fault                                       |

| 4.4.1. | Case 1: Low Resistance Fault                        |

| 4.4.2. | Case 2: High Resistance Fault85                     |

| 4.4.3. | Implementation of DCCB88                            |

| 4.5.   | Conclusion                                          |

| СН     | APTER 5: TWO-TERMINAL MMC AVERAGED MODEL-BASED HVDC |

| SYSTE  | M93                                                 |

| 5.1    | MMC Averaged Model (AVM-MMC)93                      |

| 5.1.1  | AVM-MMC: Topology and Operation93                   |

| 5.1.2  | AVM-MMC Mathematical Model95                        |

| 5.1.3  | AVM-MMC Modulation97                                |

| 5.2    | Two-terminal AVM-MMC-based HVDC System              |

| 5.2.1  | AVM-MMC Simulation Results99                        |

| 5.2.2  | <i>Two-terminal AVM-MMC Simulation Results</i> 106  |

| 5.3    | Conclusion108                                       |

| СНАРТ  | ER 6: CONCLUSION & FUTURE WORK109                   |

| 6.1    | Conclusion109                                       |

|        | ix                                                  |

| 6.2     | Future w | vork                                             | 111  |

|---------|----------|--------------------------------------------------|------|

| REFERI  | ENCES    |                                                  | .112 |

| APPENI  | DIX      |                                                  | .127 |

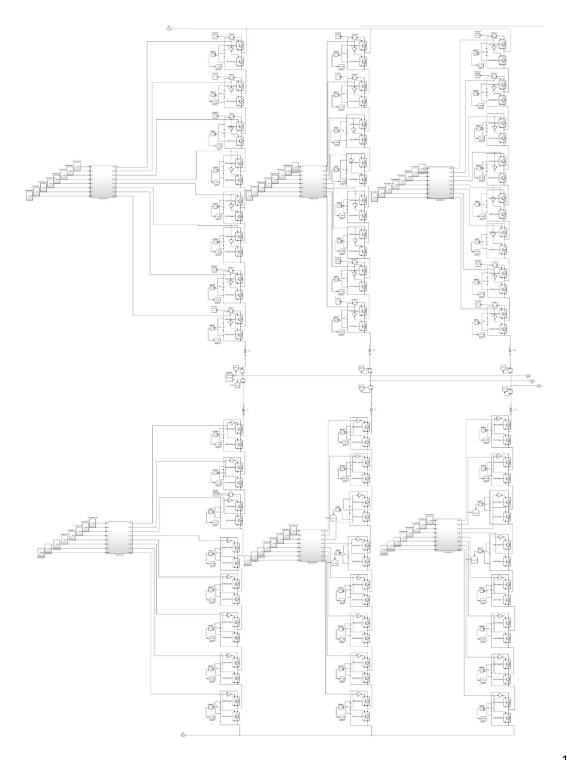

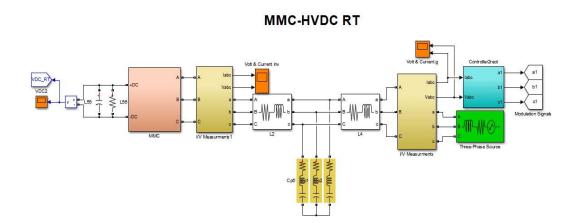

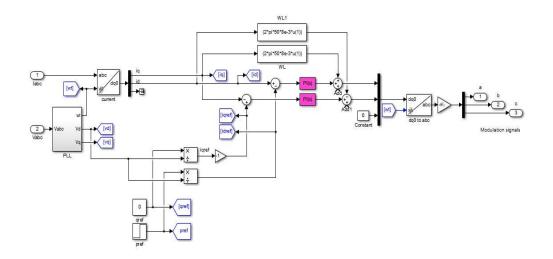

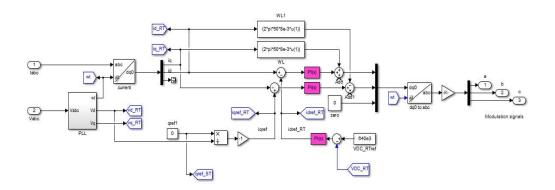

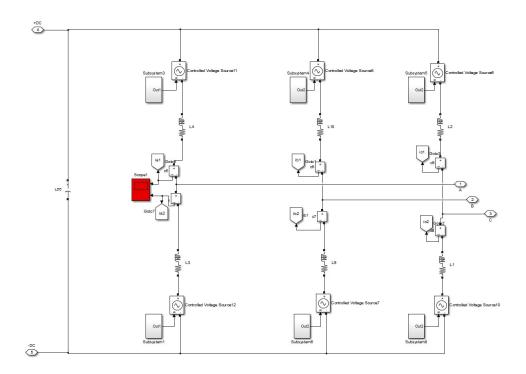

| Appendi | x A.1    | Voltage balancing technique & MMC SIMULINK MODEL | 127  |

| Appendi | x A.2    | MMC-Based HVDC system model in simulink          | .129 |

| Appendi | x A.3    | AVM-MMC Based HVDC model in simulink             | .131 |

# LIST OF ABBREVIATIONS

| HVDC            | High Voltage Direct Current                                |

|-----------------|------------------------------------------------------------|

| VSC             | Voltage Source Converter                                   |

| VSC-HVDC        | Voltage Source Converter-based High Voltage Direct Current |

| MT-HVDC         | Multi-Terminal High Voltage Direct Current                 |

| ММС             | Modular Multilevel Converter                               |

| SM              | Submodule                                                  |

| HB-SMs          | Half-Bridge Sub-Modules                                    |

| FB-SM           | Full-Bridge Sub-Modules                                    |

| HCLC            | Hybrid Current Limiting Circuit                            |

| IGBT            | Insulated Gate Bipolar Transistor                          |

| HVAC            | High Voltage Alternating Current                           |

| AVM-MMC         | Modular Multilevel Converter Averaged Model                |

| DCCB            | Direct Current Circuit Breaker                             |

| СВ              | Circuit Breaker                                            |

| LCC             | Line Commutated Converter                                  |

| CSC-HVDC        | Current Source Converter-based HVDC                        |

| PWM             | Pulse Width Modulation                                     |

| PD-PWM          | Phase Disposition Pulse Width Modulation                   |

| ST              | Sending Terminal                                           |

| RT              | Receiving Terminal                                         |

| V <sub>DC</sub> | DC link voltage                                            |

| $f_s$           |                                                            |

| f <sub>c</sub>                                                            | Corner frequency                                                                                                                                                                                                        |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL                                                                       | Phase Locked Loop                                                                                                                                                                                                       |

| $\theta_{S}$                                                              | The phase angle of the ST voltage                                                                                                                                                                                       |

| V                                                                         | The voltage amplitude of AC ST                                                                                                                                                                                          |

| $v_{S,abc}$                                                               | abc components of the sending terminal AC voltage                                                                                                                                                                       |

| v <sub>Sdq</sub>                                                          | dq components of the sending terminal AC voltage                                                                                                                                                                        |

| i <sub>S,abc</sub>                                                        | abc components of the sending terminal AC current                                                                                                                                                                       |

| i <sub>Sdq</sub>                                                          | dq components of the sending terminal AC current                                                                                                                                                                        |

| P <sub>s</sub>                                                            | Active power provided by the sending terminal                                                                                                                                                                           |

| $Q_S$                                                                     | Reactive power provided by the sending terminal                                                                                                                                                                         |

| i * <sub>sdq</sub>                                                        | Reference dq components of the sending terminal current                                                                                                                                                                 |

| <b>P</b> <sup>*</sup> <sub>S</sub>                                        | Reference active power provided by the sending terminal                                                                                                                                                                 |

| $Q_s^*$                                                                   | Reference reactive power provided by the sending terminal                                                                                                                                                               |

|                                                                           |                                                                                                                                                                                                                         |

| V <sub>R,DC</sub>                                                         | DC link voltage                                                                                                                                                                                                         |

| V <sub>R,DC</sub><br>V <sub>R,DC</sub>                                    | DC link voltage<br>Reference DC link voltage                                                                                                                                                                            |

|                                                                           | -                                                                                                                                                                                                                       |

| V <sup>*</sup> <sub>R,DC</sub>                                            | Reference DC link voltage                                                                                                                                                                                               |

| $V^*_{R,DC}$ $i^*_{Rdq}$                                                  | Reference DC link voltage<br>Reference dq components of the receiving terminal current                                                                                                                                  |

| V <sub>R,DC</sub><br>i <sub>Rdq</sub><br>P <sub>R</sub>                   | Reference DC link voltage<br>Reference dq components of the receiving terminal current<br>Active power of receiving terminal                                                                                            |

| V <sub>R,DC</sub><br>i <sub>Rdq</sub><br>P <sub>R</sub><br>Q <sub>R</sub> | Reference DC link voltage<br>Reference dq components of the receiving terminal current<br>Active power of receiving terminal<br>Reactive power of receiving terminal                                                    |

| $V_{R,DC}^*$<br>$i_{Rdq}^R$<br>$P_R$<br>$Q_R$<br>$v_{Rdq}$                | Reference DC link voltage<br>Reference dq components of the receiving terminal current<br>Active power of receiving terminal<br>Reactive power of receiving terminal<br>dq-components of the receiving terminal voltage |

| $C_f$                                                                                      | LCL filter capacitor                                                                                                  |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| L <sub>inv</sub>                                                                           | Inverter side inductor of the LCL filter                                                                              |

| L <sub>T</sub>                                                                             | Grid side inductor of the LCL filter                                                                                  |

| L <sub>lim</sub>                                                                           | DCCB limiting reactor                                                                                                 |

| L <sub>CL</sub>                                                                            | HCLC reactor                                                                                                          |

| R <sub>CL</sub>                                                                            | HCLC Resistance                                                                                                       |

| $T_{1}, T_{2}$                                                                             | HCLC Thyristor Switches                                                                                               |

| v <sub>j</sub>                                                                             | Total Phase voltage                                                                                                   |

| $v_{jl}, v_{ju}$                                                                           | Upper and Lower SMs voltages of phase <i>j</i>                                                                        |

| $I_{ju}, I_{jl}$                                                                           | Upper and Lower arm currents of phase <i>j</i>                                                                        |

| i <sub>ccj</sub>                                                                           | Circulating current of phase <i>j</i>                                                                                 |

| $v_{armuj}, v_{armlj}$                                                                     | Upper and Lower arm voltage of phase <i>j</i>                                                                         |

| i <sub>armuj</sub> , i <sub>armlj</sub>                                                    | Upper and Lower arm current of phase <i>j</i>                                                                         |

|                                                                                            | opper and Lower arm current of phase j                                                                                |

| n                                                                                          | Number of SMs per arm                                                                                                 |

| n<br>V <sub>cuj</sub> , V <sub>clj</sub>                                                   |                                                                                                                       |

|                                                                                            | Number of SMs per arm                                                                                                 |

| $v_{cuj}, v_{clj}$                                                                         | Number of SMs per arm<br>Upper and Lower arm SM capacitor voltages                                                    |

| v <sub>cuj</sub> , v <sub>clj</sub><br>C <sub>arm</sub>                                    | Number of SMs per arm<br>Upper and Lower arm SM capacitor voltages<br>Equivalent arm capacitance                      |

| v <sub>cuj</sub> , v <sub>clj</sub><br>C <sub>arm</sub><br>n <sub>u</sub> , n <sub>l</sub> | Number of SMs per arm<br>Upper and Lower arm SM capacitor voltages<br>Equivalent arm capacitance<br>Modulating signal |

# LIST OF TABLES

| Table 1: VSC-HVDC System's Parameter                     | 32 |

|----------------------------------------------------------|----|

| Table 2: Half-bridge SM working states                   | 54 |

| Table 3: Nine-Level transient model MMC parameters       | 63 |

| Table 4: Nine-Level transient MMC-HVDC system parameters | 71 |

| Table 5: AVM-MMC model simulation parameters             | 99 |

# LIST OF FIGURES

| Figure 1: EUMENA Super DC Grid interconnection map [13]                | 3  |

|------------------------------------------------------------------------|----|

| Figure 2: Breakeven Distance of HVDC against HVAC                      | 4  |

| Figure 3: ALSTOM HVDC projects worldwide [28]                          | 10 |

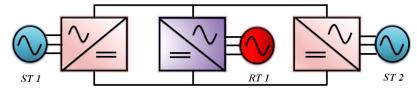

| Figure 4: Two-Terminal VSC-HVDC transmission scheme                    | 11 |

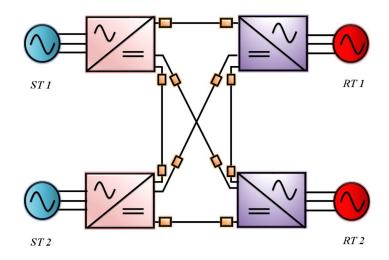

| Figure 5: Multi-terminal HVDC series configuration                     | 13 |

| Figure 6: Multi-terminal HVDC parallel configuration                   | 13 |

| Figure 7:Multi-terminal HVDC meshed configuration                      | 13 |

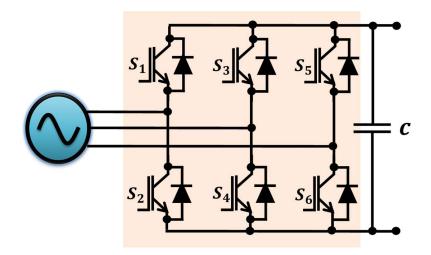

| Figure 8: Two-level VSC configuration                                  | 15 |

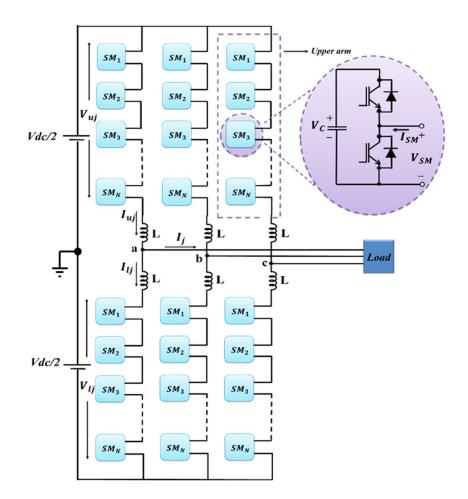

| Figure 9: Modular multilevel converter structure                       | 18 |

| Figure 10: DC side fault in two-level converter                        | 20 |

| Figure 11: FB-SM possible current paths during a DC side fault         | 20 |

| Figure 12: CD-SM possible current paths during DC side fault           | 21 |

| Figure 13: HB-SM current path during DC side fault                     | 21 |

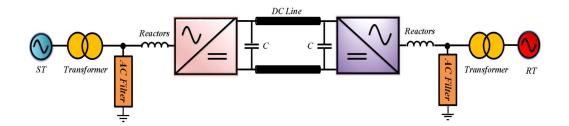

| Figure 14: Two-terminal VSC-HVDC system.                               | 23 |

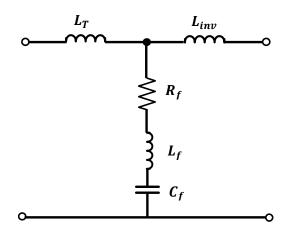

| Figure 15: LCL Passive filter used in the Study                        | 24 |

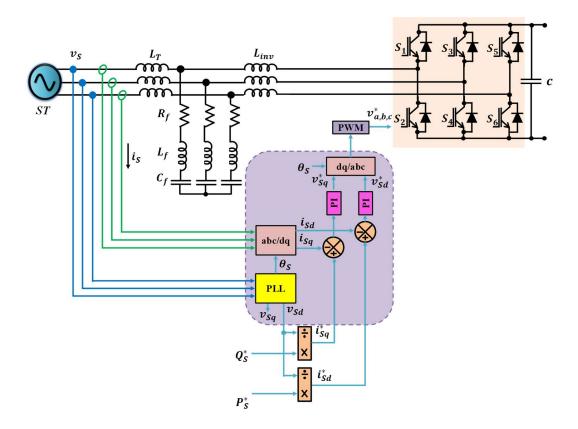

| Figure 16: Sending end control scheme                                  | 27 |

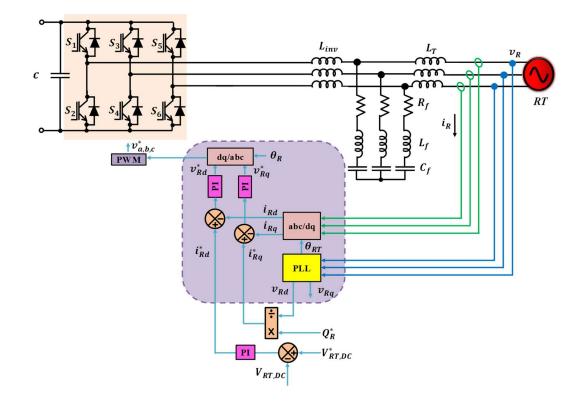

| Figure 17: Receiving end control scheme                                | 29 |

| Figure 18: Active power and reference active power at ST               | 33 |

| Figure 19: Reactive power and reference reactive power at ST           | 33 |

| Figure 20: d-component current and reference d-component current at ST | 34 |

| Figure 21: q-component current vs. reference q-component current at ST | 34 |

| Figure 22: Active and reactive powers of ST and RT                     |    |

| Figure 23: dq Currents of ST and RT                                            | 35 |

|--------------------------------------------------------------------------------|----|

| Figure 24: DC voltages of ST and RT                                            | 36 |

| Figure 25: DC current                                                          | 36 |

| Figure 26: ST Three-phase grid side current of VSC-HVDC                        | 37 |

| Figure 27: ST Three-phase voltage of VSC-HVDC                                  | 37 |

| Figure 28: RT Three-phase grid side current of VSC-HVDC                        | 38 |

| Figure 29: RT Three-Phase Voltage of VSC-HVDC                                  | 38 |

| Figure 30: VSC-HVDC pole-to-pole fault schematic diagram                       | 39 |

| Figure 31: Hybrid DC circuit breakers                                          | 41 |

| Figure 32: A pole-to-pole DC side fault at VSC-HVDC ST                         | 42 |

| Figure 33: DC link voltage during fault t=2sec                                 | 43 |

| Figure 34: DC capacitor current at DC side fault at t=2 sec                    | 43 |

| Figure 35: Inverter current during DC fault at t=2 sec                         | 43 |

| Figure 36: Fault current                                                       | 44 |

| Figure 37: Three-phase grid side current during DC fault at t=2sec             | 44 |

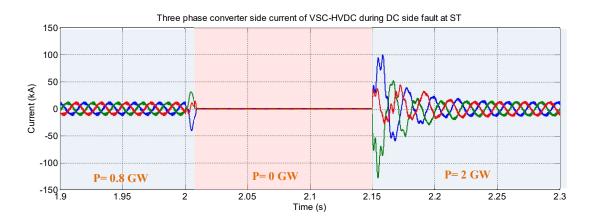

| Figure 38: Three-phase converter side current of VSC-HVDC during DC side fault | 45 |

| Figure 39: DC link voltage of ST under fault                                   | 46 |

| Figure 40: DC Capacitor current during DC side fault                           | 46 |

| Figure 41: ST DC link fault current                                            | 46 |

| Figure 42: Converter current during the DC side fault                          | 47 |

| Figure 43: Three-phase current of the ST during DC side fault                  | 47 |

| Figure 44: Three-phase converter side current during DC side fault at ST       | 48 |

| Figure 45: Fault scenario timeline                                             | 48 |

| Figure 46: DC link voltage of the ST50                                                 |

|----------------------------------------------------------------------------------------|

| Figure 47: Converter's DC current                                                      |

| Figure 48: DC link Capacitor current                                                   |

| Figure 49: ST DC link fault current                                                    |

| Figure 50: Three-phase current of the ST                                               |

| Figure 51: Three-phase converter side current during DC side fault                     |

| Figure 52: Simplified MMC configuration                                                |

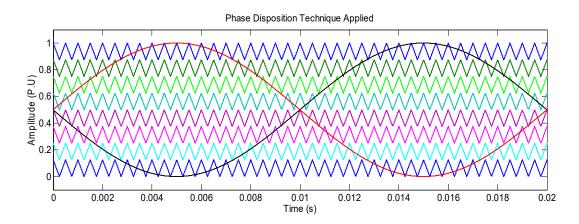

| Figure 53: 9-Level PD-PWM technique with modulation index of 1                         |

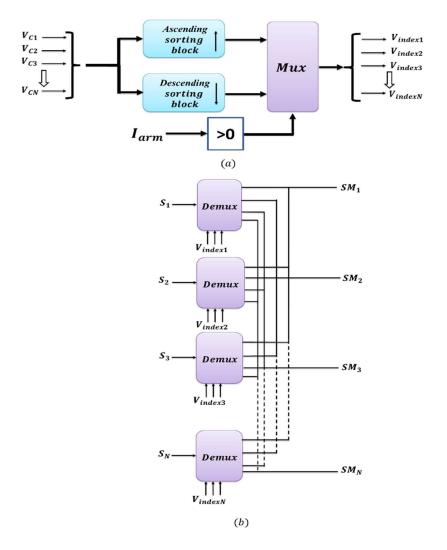

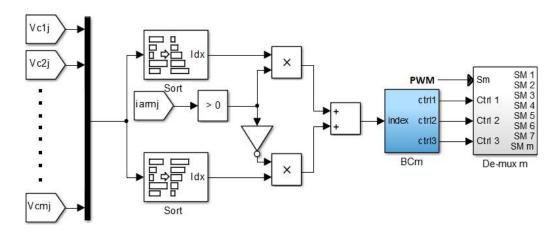

| Figure 54: Applied balancing technique (a) sorting approach (b) modulation strategy62  |

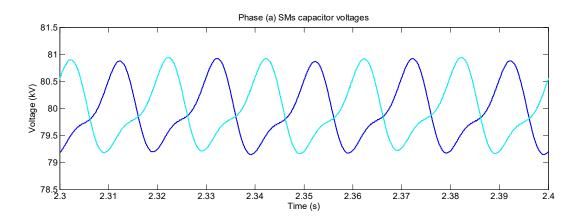

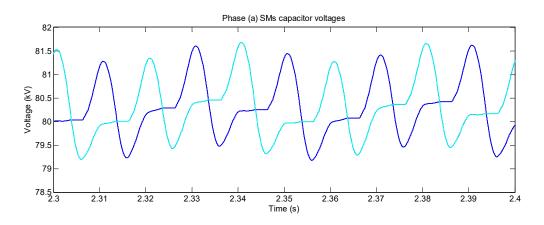

| Figure 55: Zoomed-in scale of the capacitor voltages of phase (a) at $fs = 2kHz$ 64    |

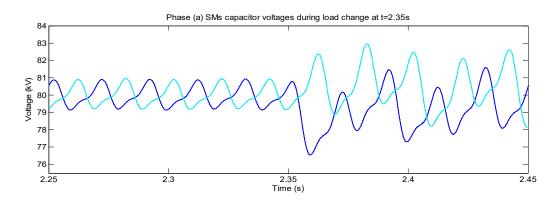

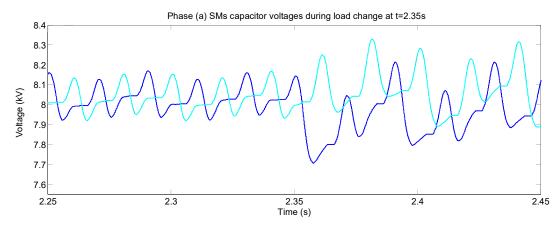

| Figure 56: SMs capacitor voltages of phase (a) in case of load change at $fs = 2kHz65$ |

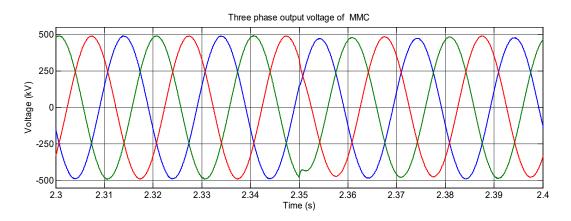

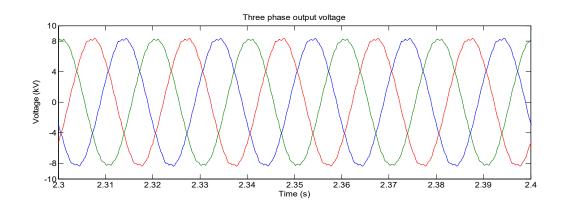

| Figure 57: Three-phase output voltage of MMC operating at 2kHz65                       |

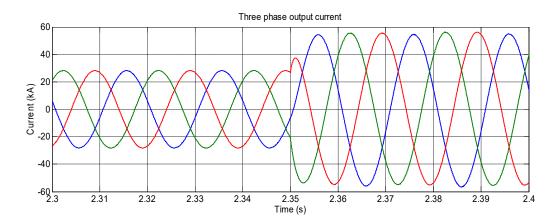

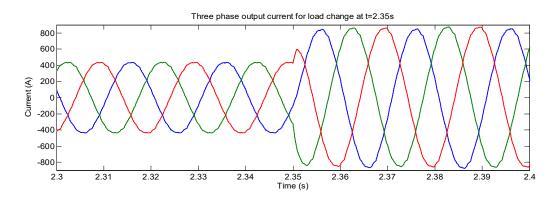

| Figure 58: Three-phase output current operating at 2kHz                                |

| Figure 59: SMs capacitor voltages of phase (a) $fs=50$ Hz67                            |

| Figure 60: SMs capacitor voltages of phase (a) in case of load change at $fs=50$ Hz67  |

| Figure 61: Three-phase output voltage of MMC at fundamental frequency                  |

| Figure 62: Three-phase output current of MMC operating at the fundamental frequency68  |

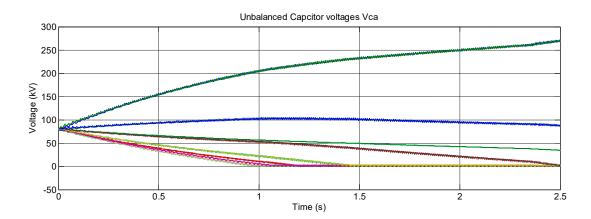

| Figure 63: SMs capacitor voltages of phase (a) without balancing                       |

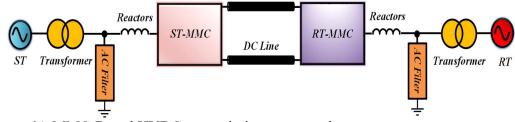

| Figure 64: MMC-Based HVDC transmission system scheme70                                 |

| Figure 65: Active power response against reference active power72                      |

| Figure 66: Reactive power response against reference reactive power72                  |

| Figure 67: d-component current against its reference73                                 |

| Figure 68: q-component current against its reference                                   |

| Figure 69: Nine-Level transient MMC three-phase grid side current of ST74           |

|-------------------------------------------------------------------------------------|

| Figure 70: Nine-Level transient MMC Three-phase voltage at ST74                     |

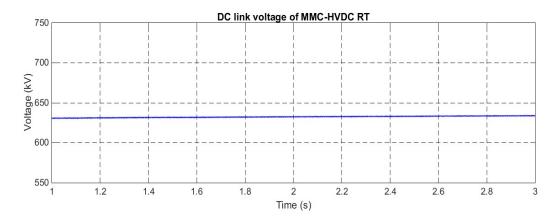

| Figure 71: DC link voltage of MMC-HVDC RT75                                         |

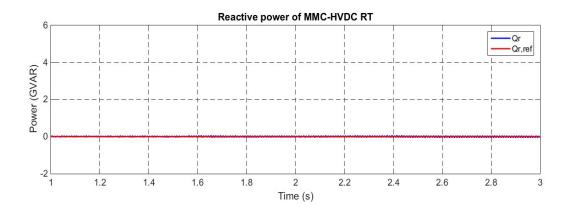

| Figure 72: Reactive power and reference reactive power of MMC-HVDC RT76             |

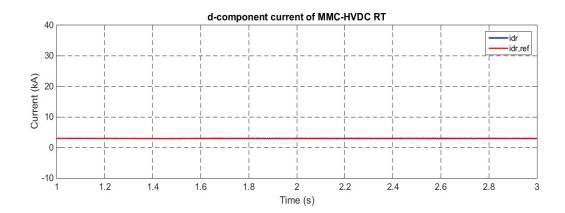

| Figure 73: d-component current and reference d-component current of MMC-HVDC RT     |

|                                                                                     |

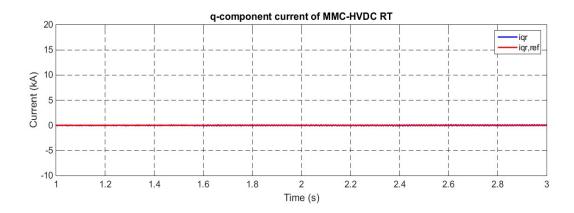

| Figure 74: q-component current and reference q-component current of MMC-HVDC RT     |

|                                                                                     |

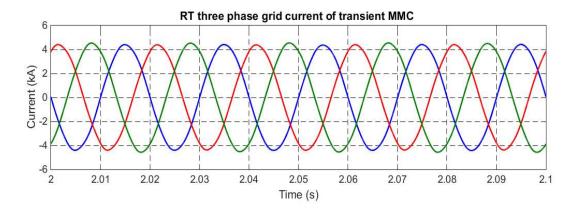

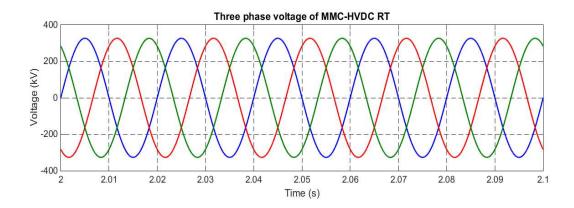

| Figure 75: Nine-Level transient MMC three-phase grid side current of RT77           |

| Figure 76: Nine-Level transient MMC three-phase voltage of RT78                     |

| Figure 77: Equivalent fault circuit during blocked SMs79                            |

| Figure 78: Hybrid current limiting circuit (HCLC)                                   |

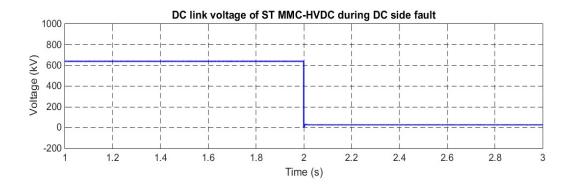

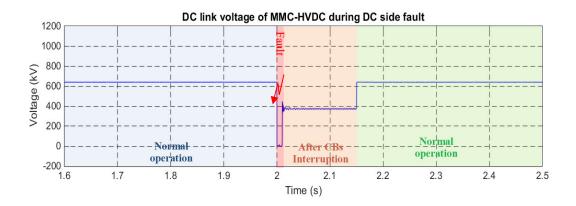

| Figure 79: DC link voltage of Nine-Level transient MMC-HVDC system during fault at  |

| ST                                                                                  |

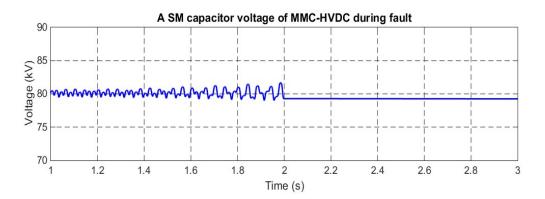

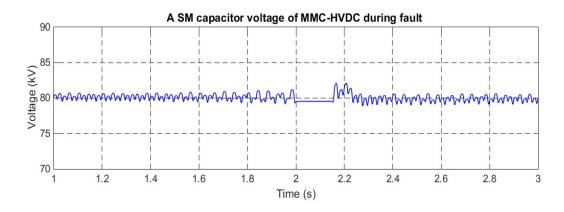

| Figure 80: SM capacitor voltage of Nine-Level transient MMC-HVDC system during      |

| fault at ST                                                                         |

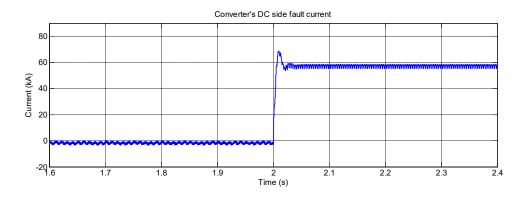

| Figure 81: Fault current of Nine-Level transient MMC-HVDC system during fault at ST |

|                                                                                     |

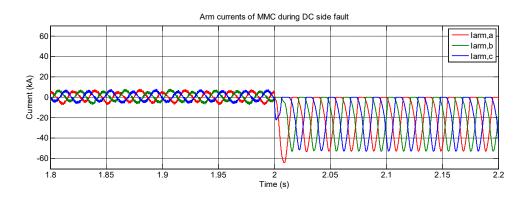

| Figure 82: Currents passing through upper arms of Nine-Level MMC-HVDC during fault  |

|                                                                                     |

| Figure 83: Three-phase grid side current of Nine-Level transient MMC-HVDC during    |

| fault at ST                                                                         |

| Figure 84: Three-phase converter side current of Nine-Level transient MMC-HVDC      |

| during fault at ST                                                                  |

|-------------------------------------------------------------------------------------|

| Figure 85:DC link voltage of Nine-Level MMC-HVDC system through high resistance     |

| fault                                                                               |

| Figure 86: A SM capacitor voltage of Nine-Level MMC-HVDC through high resistance    |

| fault                                                                               |

| Figure 87: Fault current of Nine-Level MMC-HVDC through high resistance fault86     |

| Figure 88: Currents passing through upper arms of Nine-Level MMC-HVDC at high       |

| resistance fault                                                                    |

| Figure 89: Three-phase grid current of Nine-Level MMC-HVDC at high resistance fault |

|                                                                                     |

| Figure 90: Three-phase converter side current of Nine-Level MMC-HVDC at high        |

| resistance fault                                                                    |

| Figure 91: DC link voltage of Nine-Level transient MMC-HVDC during temporary fault  |

|                                                                                     |

| Figure 92: A SM capacitor voltage of Nine-Level transient MMC-HVDC during           |

| temporary fault90                                                                   |

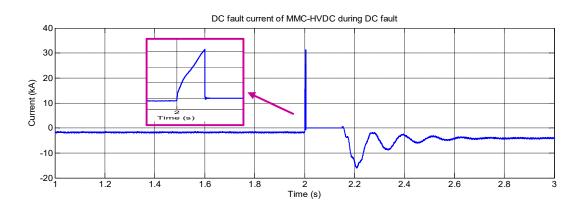

| Figure 93: DC fault current of Nine-Level transient MMC-HVDC during temporary fault |

|                                                                                     |

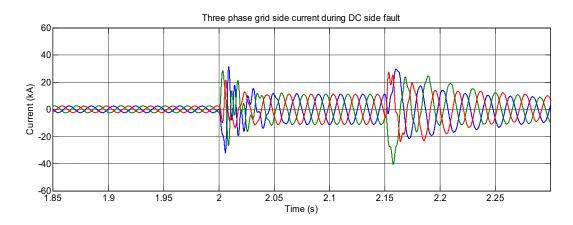

| Figure 95: Three-phase grid side current of Nine-Level transient MMC-HVDC during    |

| temporary fault                                                                     |

| Figure 96: Three-phase converter side current of Nine-Level transient MMC-HVDC      |

| during temporary fault                                                              |

| Figure 97: Three-phase MMC averaged model94                                         |

| Figure 98: 9-Level AVM-MMC (a) PD-PWM technique applied (b) arm voltage of      |

|---------------------------------------------------------------------------------|

| AVM-MMC                                                                         |

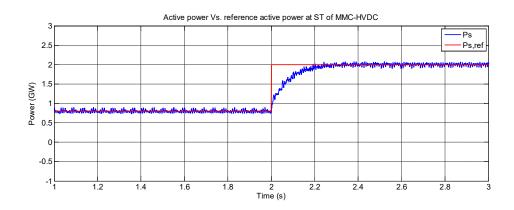

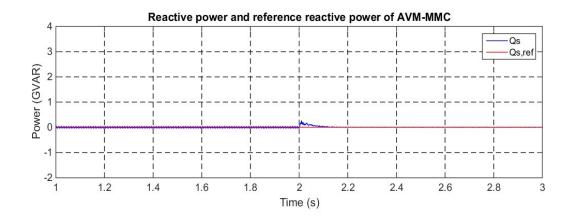

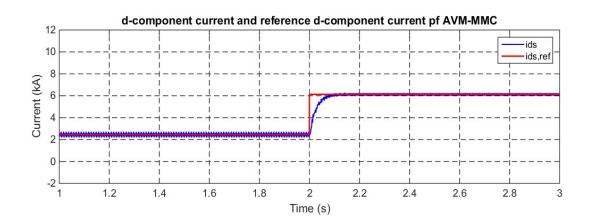

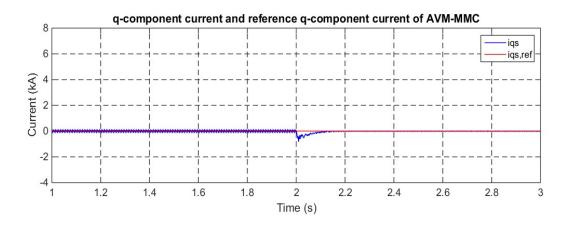

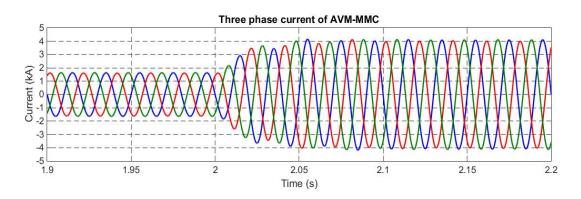

| Figure 99: Active power and reference active power of 25-Level AVM-MMC of ST100 |

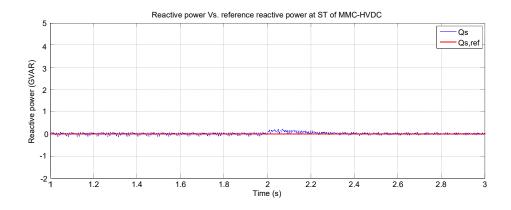

| Figure 100:Reactive power response Qs against. Qs,ref of AVM-MMC of ST101       |

| Figure 101: AVM-MMC d-component current against its reference of ST101          |

| Figure 102: AVM-MMC q-component current against its reference of ST102          |

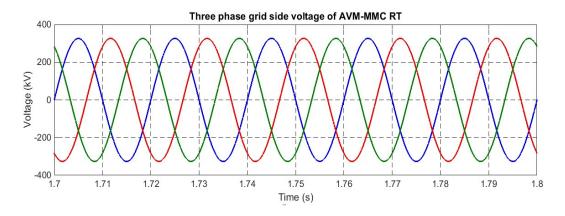

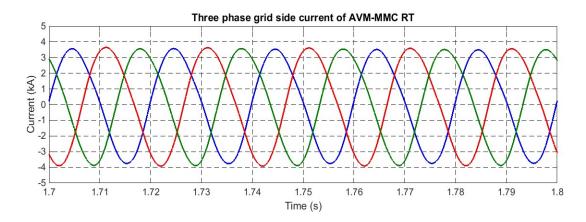

| Figure 103: 25-Level AVM-MMC three-phase current at ST102                       |

| Figure 104: 25-Level AVM-MMC three-phase voltage at ST103                       |

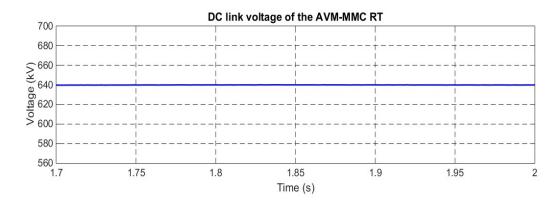

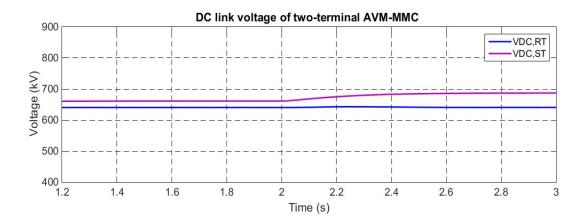

| Figure 105: DC link voltage of AVM-MMC RT104                                    |

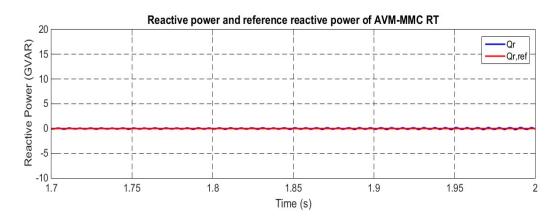

| Figure 106: Reactive power and reference reactive power of AVM-MMC RT104        |

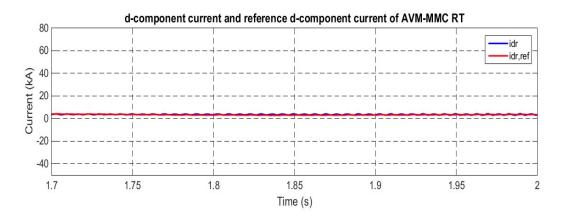

| Figure 107: d-component current and its reference at AVM-MMC RT105              |

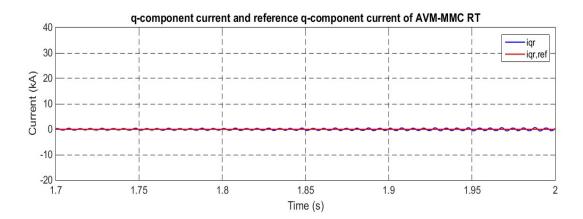

| Figure 108: q-component current and its reference at AVM-MMC RT105              |

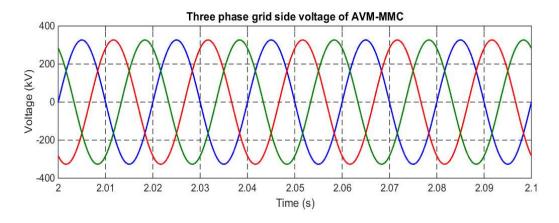

| Figure 109: 25-Level AVM-MMC three-phase grid side voltage at RT106             |

| Figure 110: 25-Level AVM-MMC three-phase grid side current at RT106             |

| Figure 111: 25-Level AVM-MMC two-terminal DC link voltage107                    |

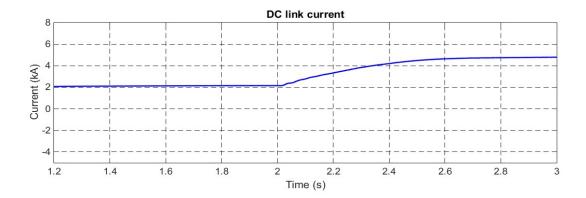

| Figure 112: 25-Level AVM-MMC two-terminal DC link current                       |

#### **CHAPTER 1: INTRODUCTION**

## 1.1. Background

Power transmission systems have experienced a development process from DC with Edison DC generators to AC and then to hybrid AC/DC transmission systems [1], [2]. Originally, DC transmission systems were not the best technical solution, as the technology was primitive and suffers from several drawbacks such as the absence of DC-DC transformers, which led to transferring power at low voltage levels over short distances [2]. Thus, the AC system was then adopted worldwide to operate power systems, as transformers allows stepping up the voltage level while transmitting power, to minimize the system losses [2]. Nevertheless, increasing the power demand, showed a number of concerns related to the AC transmission system such as synchronized operation of synchronous machines, voltage drop because of the transmission line reactance, transient stability and voltage stability [2]. Therefore, developing power transmission systems have become the main concern especially for long distances. Consequently, High-Voltage Direct Current (HVDC) technology was introduced and first used in 1954 in the under-sea cable interconnection between the island of Gotland (Sweden) and Sweden. In this HVDC transmission system, thyristors of the ratings 50 kV and 100 A were used [3]. Since 1954 until the mid of 1970s, the HVDC transmissions were based on mercury arc valves. However, in the following years, line commutated converters using thyristors were used in HVDC transmission systems [3],[2]. In 1990's, with the development of high-power semiconductor switches (specially Insulated-Gate Bipolar Transistors (IGBTs)) and their availability at affordable prices, self-commutated converters (typically Voltage Source Converters (VSCs)) have been used for HVDC transmission, where the first VSC-HVDC

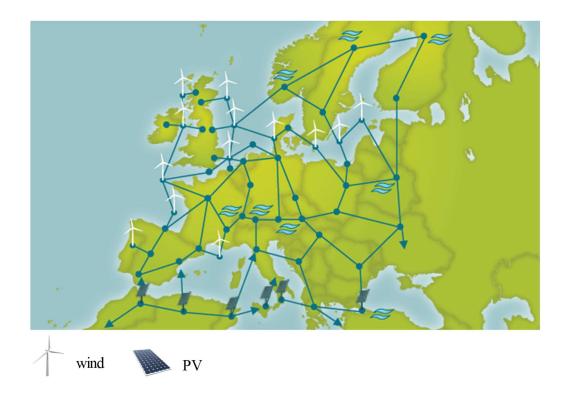

link came in service in 1999 [2],[3]. HVDC systems are considered a preferable technical solution for long cable connections compared to High-Voltage Alternating Current (HVAC) systems, because of the high charging current of AC cables. Also, the power oscillations of an AC grid can be damped by the fast modulation of the DC transmission system, and hence, improve the system stability [4], [5]. Furthermore, HVDC transmission systems offer fast and accurate control of power flow in contrast to HVAC systems. Another advantage of HVDC transmission systems is that inductive and capacitive parameters of overhead lines or cables do not limit the transmission capacity or the transmission distance unlike AC transmission links [5], [4]. In addition, HVDC transmission allows the connection of two AC systems of same or different frequencies [4],[5],[6]. The HVDC system is a highly efficient alternative for transmitting large amounts of power over long distances and for special purpose applications. As the future energy system is based on renewable energy sources, HVDC truly models the grid of the future [4] as, some renewable energy sources are located far away from the consumption area. For example, the installation of large-scale offshore wind farms [7], and the integration of solar energy in the Middle East and North Africa for the interconnection of Europe super DC grid (EUMENA) by 2050 as shown in Figure 1 in order to supply about 15% of the European electricity demand [8]. For such projects, HVDC transmission systems are technically and economically efficient more than HVAC systems [9]. Moreover, offshore power transmission using submarine cables became a crucial source for large-scale renewable energy sources because of the high wind speeds in offshore areas resulting in 70% energy greater than onshore [4]. The installation and connection of such offshore wind farms to the grid over long distances became much powerful and efficient using VSC-HVDC transmission systems [10]. In addition, submarine power transmission cables have improved its capacity [11]. For example, the Basslink cable installed in 2005, was the world's longest HVDC cable at that time. However, a 580 km submarine cable in Norway – Netherlands system was completed in 2008 [11], [12]. Further improvements in submarine cable and interconnected grids encourage the mitigation of grids interconnection challenges.

Figure 1: EUMENA Super DC Grid interconnection map [13]

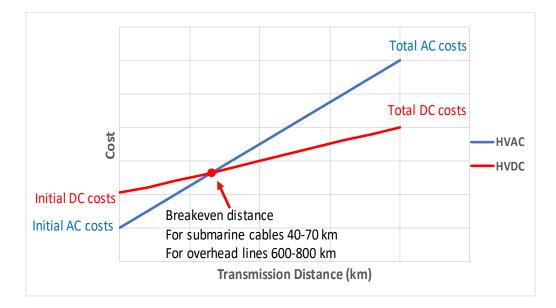

From an economical point of view, and for short distances, HVAC systems are superior to HVDC, and this is basically due to the need for AC-DC and DC-AC converter stages in

HVDC. However, for long distances, HVDC systems are advantageous because HVAC transmission requires reactive power compensation, consequently more cost [3],[4],[5],[6]. Hence, the breakeven point is in the range of 40-70 km for submarine cables for the application of offshore wind energy in HVDC, and in the range of 400-800 km for overhead lines as displayed in Figure 2 [14].

Figure 2: Breakeven Distance of HVDC against HVAC

As a conclusion to this comparison, HVDC transmission technology is attractive and advantageous for long power transmissions, bulk power delivery, submarine power and asynchronous interconnections [4], [15].

### 1.2. Thesis Objective

The objective of this thesis is to investigate and model a point-to-point VSC-based HVDC transmission system using Modular Multilevel Converter (MMC) transient model, and MMC averaged model. Considering the requirements of HVDC systems such as HV requirements and fault ride through capability. The design of the MMC transient model in this study is based on Half-Bridge Sub-Modules (HB-SMs) because of its simple structure. However, other structures are discussed highlighting their pros and cons. Nevertheless, balancing of the floating capacitors is one of the challenges associated with MMCs, therefore capacitor voltage balancing, and its modeling is tackled. Then the average model of the MMC-based HVDC systems. Also, the behavior during DC side faults is investigated, and the employment of hybrid DC circuit breakers and Hybrid Current Limiting Circuit (HCLC) are addressed. This introduces a platform for investigating and studying MMC-based HVDC systems in normal operation and during faults.

The thesis contribution can be stated as follows:

• Surveying and modeling of conventional VSC-based point-to-point HVDC systems

• Building a transient model for MMC-based point-to-point HVDC system considering nine-level as a case study.

• Building of an Averaged MMC model (AVM-MMC) considering 25-level as a case study.

• Building of a point-to-point VSC-HVDC transmission system model using an AVM-MMC.

• Employment of High-voltage DC side protection using hybrid DC Circuit Breakers (DCCB) and Hybrid Current Limiting Circuit (HCLC).

## 1.3. Thesis Outline

The thesis report is structured firstly with an introductory overview of the requirements and the importance of HVDC transmission systems in chapter 1. This is followed by a literature survey on the history of HVDC systems and their topologies in chapter 2. A twoterminal two-level converter-based HVDC system model is presented, and a DC side fault is introduced to the HVDC system in chapter 3. In chapter 4, a model of the two-terminal MMC-based HVDC system is presented as well as, a comprehensive study and modeling of HB-MMC including balancing the SM capacitor voltages. In addition to studying the MMC-HVDC under DC side fault, an MMC Averaged Model (AVM-MMC) is presented, and a two-terminal AVM-MMC HVDC is studied in chapter 5. Chapter 6 presents a comparison between the different VSC topologies introduced in this study to model a backto-back or point-to-point HVDC transmission system. Finally, conclusions and further improvements are presented.

### CHAPTER 2: VSC-BASED HVDC SYSTEMS

### 2.1 VSC-HVDC Systems

HVDC transmission systems are considered a promising power transmission technology, especially for long distances. With the great development of the VSC technologies (namely topologies, control, and semiconductor devices), the field of applications of VSC-HVDC transmission systems and Flexible AC Transmission Systems (FACTS) are expanded in power systems. VSC-HVDC systems combine VSC with DC transmission lines to transmit power up to several GWs [16]. VSC-HVDC is considered one of the preferred solutions for DC interconnections, Multi-Terminal Direct Current (MT-HVDC) transmission, and installation of offshore wind power generation [15], [17-20]. VSC-HVDC systems are superior to classical HVDC systems (i.e. line commutated converters HVDC systems) for the following advantages [3], [5],[21-25]:

• It can independently control active and reactive powers at both terminals by sustaining stable voltage and frequency [22], which enables the supply of weak grids and even passive networks [16].

• The commutation failures caused by disturbances in the AC network can be avoided by using VSC-HVDC technology [3], [21], [23].

• Black start capability [5].

• VSC technology does not require large AC filters, which enables the design of compact converter station [24].

• As it has a standardized construction, the converter system can be easily installed and replaced [5].

### 2.1.1. Applications of VSC-HVDC systems

The HVDC market is growing rapidly and has become an important part of many transmission grids through overhead lines and submarine cables. It allows the connection of remote generations, interconnecting grids, connecting offshore wind turbines, connecting remote loads, transmitting power from offshore and stabilization of power flow. ABB is a leading company in the field of HVDC systems, for more than 60 years of HVDC experience and more than 170 projects worldwide [4]. Several VSC-HVDC systems developed by ABB under the name HVDC Light. Some recent projects of ABB are listed here [4]:

• BorWin1, which is one of the most remote offshore wind farm generations in the world, has been connected to the German grid through 400 MW +/- 150 kV two-level VSC-HVDC in 2010.

• Also in Ireland, ABB has grid-integrated a 500 MW two-level VSC-HVDC through +/-200 kV submarine cables in 2013. This HVDC link provides an opportunity to export excess power into the UK market.

• Moreover, ABB is integrating a 410 MW HVDC station that connects Kriegers Flak offshore-grid to the German grid in Bentwisch, northern Germany by the end of 2018. This interconnection through HVDC system helps securing the energy supply in Denmark and supports the energy trading in Germany.

• ABB is integrating the first 1,100 kV UHVDC power link in China that transmits power from the Xinjiang region in the Northwest, to Anhui province in eastern China, and sets a new world record in terms of voltage level, transmission capacity and distance in 2016. This system is capable of transmitting 12 GW over a distance of around 2000 km– 3000 km. This facilitates transmitting power over greater distances and grid interconnection.

Another leading company in the HVDC market is Siemens. VSC-HVDC systems developed by Siemens are called HVDC Plus ("Plus" -Power Link Universal Systems) [26], which have projects worldwide such as [22]:

• ALEGrO interconnector project: installing the two MMC-HVDC converter stations for the first electricity interconnection between Germany and Belgium along 90 km distance with a capacity of 1000 MW through underground cable by 2020.

• ElecLink interconnector project: to increase the capacity of the existing interconnection between Britain and France by 50%, using MMC-HVDC system with a rating of 1000 MW and  $\pm 320$  kV DC link, linked by a 51 km long DC power cable, which will be fully commissioned by 2020.

ALSTOM is another leading company in HVDC and UHVDC market for over 50 years, which plays a role in the development of HVDC networks and connections in the coming years [27]. The company has delivered more than 40 projects over the world. Some of the projects developed by ALSTOM worldwide are as presented in Figure 3 and the following points:

Figure 3: ALSTOM HVDC projects worldwide [28].

• In 2015, ALSTOM was awarded a contract to build an HVDC transmission link between France and Italy using ALSTOM's VSC MaxSine technology which is MMC technology with ratings of  $2 \times 600$  MW of power and  $\pm 320$ kV voltage level.

• ALSTOM has installed a multi-terminal HVDC grid from Sweden's south-west link to central and southern networks of Sweden using ALSTOM's VSC MaxSine technology (MMC) by 2014 for a total distance of 250 km delivering power of 1440 MW and  $\pm 300$  kV voltage level.

• The Dolwin3 HVDC project using ALSTOM's VSC MaxSine technology (MMC) to install the third grid in the Dolwin cluster connecting 900 MW offshore wind energy from the North Sea to the German grid over a distance of 162 km by 2017.

## 2.1.2. VSC-HVDC system structure

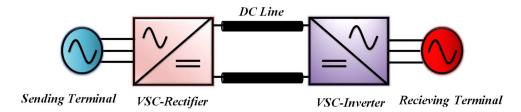

VSC is the main block for a specific class of HVDC converters. The first generation technology uses two-level or there-level converters, because of the simple structure and less capacitors. However, this configuration suffers from the series connection of semiconductor devices' problems (static and dynamic voltage sharing), high switching losses, high *dv/dt*, hence introduces high harmonic levels and poor output voltage waveform [28], [29-30]. The basic configuration of a VSC-HVDC system is the two-terminal HVDC system. This configuration consists of two VSC stations linked by a DC transmission line as shown in Figure 4. Mainly, there are two schemes for two-terminal HVDC transmissions, which are point-to-point scheme and back-to-back scheme. Point-to-point transmission is used for long distances transmission through overhead line, underground or submarine cables also for grid interconnection between asynchronous AC systems [31]. However, back-to-back transmission scheme is mostly used to link two asynchronous AC systems at the same station.

Figure 4: Two-Terminal VSC-HVDC transmission scheme

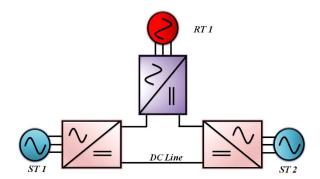

Similarly, an MT-HVDC system can be implemented but using more than two VSC stations. There are three main configurations for MT-HVDC transmission, which are series, parallel, and meshed configurations as shown in Figure 5, Figure 6, and Figure 7, respectively. The parallel configuration has several advantages when compared to the series configuration such as less insulation complexity and more reliability in case one of the converters is lost. Therefore, in practice parallel configuration is highly preferred [2]. On the other hand, the meshed HVDC topology is used when more than three converter stations are interconnected through DC link. This topology provides some benefits as higher reliability. Also, meshed topology provides increased transmission capacity. However, the enhancement of the meshed HVDC topologies has been braked by the unavailability of the HVDC Circuit Breakers (CBs) in the market. Nevertheless, ABB has introduced hybrid HVDC CB as in [31], [32] thus; it is expected that the meshed topology will be utilized as the HVDC CBs are improved. Although, MT-HVDC is out of the thesis scope, the contribution presented in the thesis provides a platform for studying such complicated systems.

Figure 5: MT-HVDC series configuration

Figure 6: MT-HVDC parallel configuration

Figure 7: MT-HVDC meshed configuration

### 2.2. Two-Level Inverter HVDC system

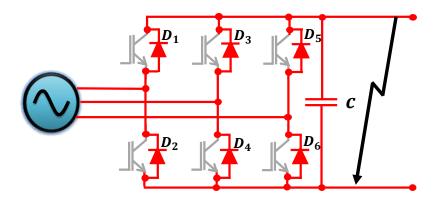

The development of the VSC technologies with off-the-shelf semiconductor devices is significantly expanding the applications of HVDC transmission systems. The first generation of VSC-HVDC has been introduced and manufactured by ABB [33]. This generation utilizes the two-level converter topology. This topology is the basic configuration of a VSC. It consists of six semiconductor devices (mostly IGBTs) with their six antiparallel diodes as shown in Figure 8. The drawbacks of this configuration are that it produces high harmonic distortion, and it causes high stresses on the switches especially in HVDC applications due to HV requirements. Typically, a series connection of multiple IGBTs allows meeting the requirements of high DC transmission voltage [33], [34]. However it introduces another problem, which is the voltage sharing of the switches at both static and dynamic phases. Therefore, multilevel converters have attracted significant interest in the last three decades, particularly for high power applications. Typically, multilevel converters consist of semiconductor devices, and voltage clamping approaches as isolated power supplies in cascaded H-bridge multilevel converter, didoes in diode-clamped multilevel converter [35], [36] and capacitors in flying capacitor multilevel converter [37], [38]. Nevertheless, increasing the number of levels increases the complexity of control and implementation [39]. Based on this, a new type of multi-level converters, Modular Multilevel Converter (MMC) [40], [41] has been developed to overcome the limitations of other multilevel converters specially in high power applications, considering the requirements of semiconductor devices and passive elements, the required isolated DC supplies, modularity, and capacitor voltages' balancing. Therefore, MMC is advantageous due to its scalability, modularity, and fault ride through capability [42],[43],[44].

Figure 8: Two-level VSC configuration

#### 2.3. MMC-Based HVAC

## 2.3.1. MMC

MMC is considered as a potential candidate for high power applications, due to its modularity and scalability. In addition, filter requirements can be significantly reduced by using a high number of levels per phase [16]. Scalability to higher voltages is easily achieved, and reliability is improved by increasing the number of SMs per arm [45]. Also, conventional VSCs use concentrated reservoir capacitors at the converter DC input, while MMC uses distributed capacitors that improve the flexibility of the VSC-HVDC transmission systems [46]. For the aforementioned reasons, MMC has become the preferred topology for large-scale HVDC links and DC grids that could ensure safe and

reliable operation during AC and DC network disturbances [46].

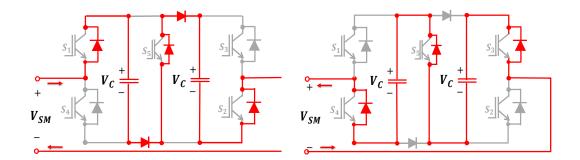

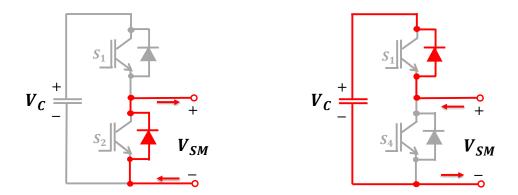

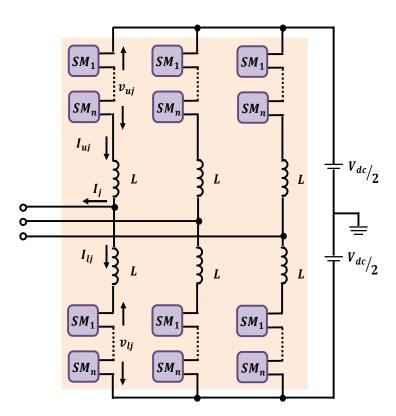

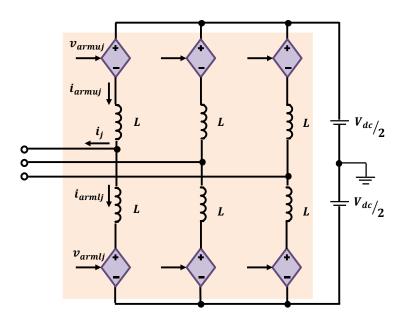

MMC employs multiple SMs connected in series from their AC side terminals in order to construct a multilevel AC voltage waveform. Each phase or leg has upper and lower arms; each arm is constructed by (N-1) SMs connected in series for N-level MMC. Every arm has an inductor to protect the switches from the inrush current caused by the capacitors as well as to limit the circulating current during normal operation [47]. In general, the number of cells in an MMC is dependent on the DC link voltage and the ratings of each cell. SMs can be constructed using Half-Bridge SM (HB-SM) [48],[49], Full-Bridge SM (FB-SM) [48],[49], Clamped Diode SM (CD-SM) [49], Switched Capacitor SM (SC-SM) [48] or other combined topologies as in [48]. The typical structure of an MMC is shown in In this study, HB-SMs are used to model the MMC. Each HB-SM is a simple chopper cell composed of two semiconductor devices  $S_1$  and  $S_2$ , two anti-parallel diodes  $D_1$  and  $D_2$ , and a capacitor C.

Due to the required enormous number of cells in MMC for HVDC applications, MMC modeling has been addressed widely in the literature. In [50], an improved transient simulation model for the HB-SM and FB-SM-based MMCs that can be used for full-scale simulation of HVDC transmission systems, with hundreds of cells per arm, has been introduced. In [51], the dynamic performance of MMC-based, back-to-back HVDC system using Phase Disposition (PD) Sinusoidal Pulse Width Modulation (SPWM) strategy, including a voltage balancing method, for the operation of an MMC has been presented. However, in [52] a comparative study of the dynamic performance of conventional VSC-HVDC and MMC-based HVDC operating in back-to-back configuration has been addressed. Furthermore, a novel high frequency conducted Electro-Magnetic Interference

(EMI) for an MMC-based HVDC system has been proposed in [53]. Based on the proposed model, the influence of parasitic parameters of the switches and the switching frequency on the leakage current has been also studied in detail. In this thesis, a point-to-point VSC-based HVDC transmission system using MMC transient model and AVM-MMC-based HVDC systems are modeled and simulated using MATLAB/Simulink platform, where the design of the MMC transient model in this study is based on HB-SMs. Hence, SM capacitor voltage balancing and its model is addressed. Also, the behavior during DC side faults is investigated, and the employment of hybrid DC circuit breakers and Hybrid Current Limiting Circuit (HCLC) are addressed as in the following chapters.

Figure 9: Modular multilevel converter structure

### 2.3.2. MMC during fault at DC side

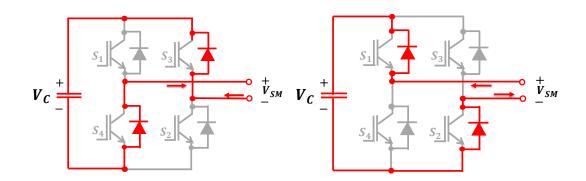

HB-SMs and FB-SMs are commonly used SMs in MMCs. Generally, HB-SM is the simplest configuration. Hence it offers less losses and lower cost. The FB-SM is well known for its bi-direction AC voltage, and most importantly, it offers blocking capability for the contribution of AC side current due to a fault in the DC side. Unlike, the HB-SM and the conventional two-level VSC, where a DC short circuit fault is a critical scenario for VSCs [54].

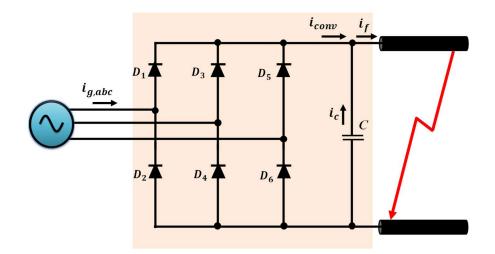

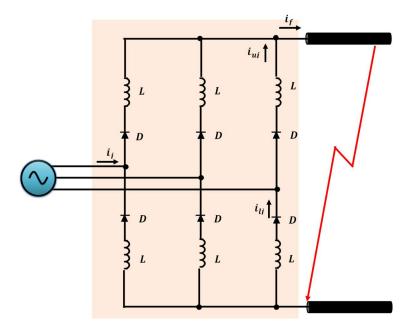

The effect of DC side faults on the conventional two-level VSC-HVDC system has different analysis from the one based on MMC. In the case of two-level VSC, the IGBT switches are blocked for self-protection, leaving the freewheeling diodes subjected to overcurrent due to the AC grid current contribution into DC fault as shown in Figure 10 [48-50],[55]. An overview of the present methods for VSC system protection has been studied in [4], [55]. Based on this, DC Circuit Breakers (CBs) are required to protect the system. However, DC CBs for HV applications are not mature as AC HV CBs [54], [55]. Another alternative, in this case, is the installation of press-pack thyristors at the AC side of the system, in order to share the short-circuit current with the diodes until the AC CBs trips, as thyristors are known for their capability to withstand surge current [54-57]. But, also AC CBs are not considered fast enough, and the power electronic devices can be damaged because of the increase in the fault current [56].

On the other hand, MMC is more advantageous when compared to conventional and other multilevel VSCs, as some SMs are defensive against DC side faults such as: FB-SM [54], CD-SM [55], SC-SM, mixed cells-based MMC [8], [9], [54], boost/buck-boost SM [54], [49]. These SMs have the ability to suppress the DC side fault because of the existence of opposing capacitor voltage after the IGBTs are turned off due to the fault such as FB-SM and CD-SM shown in Figure 11 and Figure 12 [54], where, the figures show the different current paths in each topology during the fault. It is clear that the SM capacitor is included in all paths except in the HB-SM topology, which explains why some SMs have fault blocking capability among others. But, this is at the expense of a large number of employed switches, which increases the losses, cost, and size [49], [58]-[59]. Nevertheless, HB-SM-based MMC is one of the most promising HVDC converters, although HB-SM does not

have the ability to inherently block the DC fault current. When DC fault is detected, and IGBTs are switched off typically the diodes are exposed to high fault current due to the contribution of the AC grid current as illustrated in Figure 13. To limit this, a proper design of the arm inductor can help avoiding this issue in MMCs [54]. Yet, HVDC CBs will be a necessity for interrupting the fault.

Figure 10: DC side fault in two-level converter

Figure 11: FB-SM possible current paths during a DC side fault

Figure 12: CD-SM possible current paths during DC side fault

Figure 13: HB-SM current path during DC side fault

# 2.4. Conclusion

In conclusion, in this chapter the VSC-based HVDC system has been addressed, and the advantages of VSC-HVDC over the classical HVDC using LCC have been identified, highlighting, some of the recent worldwide projects that have been developed by the major

companies in the area of HVDC systems such as ABB, Siemens, and ALSTOM. Also, the typical structure of a VSC-HVDC has been discussed, including modeling of VSC topologies used in this study which are a two-level converter, and detailed MMC. Furthermore, studying the dynamic behavior during DC side faults.

#### CHAPTER 3: TWO-TERMINAL TWO-LEVEL VSC-BASED HVDC SYSTEM

Two-terminal VSC-HVDC system can be implemented using different types of VSCs (two-level or multilevel VSCs). This chapter studies the implementation of the conventional two-level VSC in two-terminal HVDC systems. In addition, MMC and AVM-MMC are studied in the following chapters.

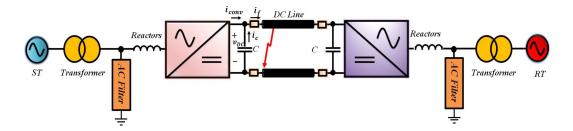

### 3.1. System overview

The two-terminal bipole HVDC system basically consists of two back-to-back connected VSCs, transformers, phase reactors, AC filters, DC capacitors, and DC transmission lines as shown in Figure 14. Two-level VSC technology is widely used in many applications at a wide range of power. This converter is constructed from six IGBTs connected with antiparallel diodes as illustrated earlier in Figure 8. It is capable of generating two output voltage levels  $\pm V_{DC}$ , where  $V_{DC}$  is the DC voltage. One converter operates as a rectifier in the Sending Terminal (ST) and the other as an inverter in the Receiving Terminal (RT). Several PWM techniques can be used for VSCs to generate the desired switching pattern.

Figure 14: Two-terminal VSC-HVDC system.

Second, transformers are required to connect the VSC to the grid. Most importantly, phase

reactors and AC filters have to be installed, in which phase reactors reduce the AC current harmonics caused by the switching operation of the VSCs [60]. However, high pass filter is tuned and installed to mitigate the high order current harmonics generated by the converters [60]. The passive filter implemented in this study acts as an LCL filter with embedded high pass filter. This is because of the existence of the transformer's leakage inductance as in Figure 15, where  $L_{inv}$ ,  $L_T$ ,  $L_f$ ,  $R_f$ , and  $C_f$  are inverter side inductance (reactor), transformer's inductance, and shunt high pass filter inductance, resistance and capacitance, respectively.

Figure 15: LCL Passive filter used in the Study

The high pass filter is tuned at both switching frequency  $f_s$  as in (1), and the LCL filter is tuned at corner or resonance frequency  $f_c$  as in (2) [61],[62]:

$$f_s = \frac{1}{2\pi\sqrt{L_f C_f}} \tag{1}$$

24

$$f_c = \frac{1}{2\pi \sqrt{\frac{L_{inv}L_T}{L_{inv} + L_T}C_f}}$$

(2)

Moreover, DC capacitors are used to keep the power balance between transients and reduce the voltage ripples on the DC side that is caused by the switching action [60]. Finally, backto-back connected VSCs are connected through DC transmission line. DC transmission lines are considered an essential link in HVDC transmission systems. In a transmission line, the resistance, inductance, and capacitance are uniformly distributed as cascaded  $\pi$  network representation along the line. However, in steady state ,a resistor can be used to represent the DC transmission line [60],[63].

### 3.2. Control of Two-terminal two-level VSC-based HVDC system

A two-terminal VSC-HVDC system is mainly used to transmit power from one AC network known as Sending Terminal (ST) to another AC network known as Receiving Terminal (RT). The power flows from the ST, which is rectifier towards the RT, which is inverter. This study adopts the method of coordinate transformation from three-phase stationary frame to two-phase synchronously rotating reference frame, i.e. dq-axes, that are then converted back to three-phase coordinates. The generated continuous signal is the modulation signal that is used later to perform the Sinusoidal Pulse Width Modulation (SPWM) that controls the semi-conductor switches used (i.e. the IGBTs). The cascaded control structure used provides tracking, as the objective of the inner control loops is to adapt with the reference dq currents at both the sending and receiving terminals in order to exchange the desired amount of power between both terminals. Nevertheless, the outer

control loop produces the reference dq currents based on the reference powers and DC link set in order to regulate the actual dq currents to be equivalent to the reference values.

### 3.2.1. Control of Sending Terminal Converter

The main advantage of VSC-HVDC systems is that it provides independent control of active and reactive powers. The ST generally can be connected to an AC grid or offshore wind energy system; however, it is represented here typically as AC grid. The ST mainly is responsible for controlling the active and reactive powers. Therefore, the three-phase currents and voltages are transformed to dq reference frame using Park's transformation as in (3-4). Using the dq reference frame gives the advantage of decoupling the active and the reactive powers, where the d-component is responsible for the active power transfer. However, q-component is responsible for the reactive power transfer. The final step of the control is to transform the d and q components into three-phase quantities as illustrated in Figure 16.

Figure 16: Sending end control scheme

The AC network of the ST is represented by equation (3)

$$v_{S} = \begin{bmatrix} v_{Sa} \\ v_{Sb} \\ v_{Sc} \end{bmatrix} = V \begin{bmatrix} \sin(\theta_{S}) \\ \sin(\theta_{S} - \frac{2\pi}{3}) \\ \sin(\theta_{S} + \frac{2\pi}{3}) \end{bmatrix}$$

(3)

Where  $v_{Sa}$ ,  $v_{Sb}$ ,  $v_{Sc}$  are the ST three-phase voltages,  $\theta_S$  is the phase angle of the ST voltage, and V is the voltage amplitude.

Applying Park-Clarke transformation, to convert the three-phase stationary reference frame abc to the two-phase rotating frame dq. Equation (4) represents the abc to dq transformation, in which the zero component is zero as it is a three-wire three-phase balanced system [60], [62].

$$v_{Sdq} = \begin{bmatrix} v_{Sd} \\ v_{Sq} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \sin(\theta_S) & \sin(\theta_S - \frac{2\pi}{3}) & \sin(\theta_S + \frac{2\pi}{3}) \\ \cos(\theta_S) & \cos(\theta_S - \frac{2\pi}{3}) & \cos(\theta_S + \frac{2\pi}{3}) \end{bmatrix} \begin{bmatrix} v_{Sa} \\ v_{Sb} \\ v_{Sc} \end{bmatrix}$$

(4)

Where  $v_{Sd}$ ,  $v_{Sq}$  are the dq components of the ST voltage. Similarly, the dq components of the currents are obtained as in (5):

$$i_{Sdq} = \begin{bmatrix} i_{Sd} \\ i_{Sq} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \sin(\theta_S) & \sin(\theta_S - \frac{2\pi}{3}) & \sin(\theta_S + \frac{2\pi}{3}) \\ \cos(\theta_S) & \cos(\theta_S - \frac{2\pi}{3}) & \cos(\theta_S + \frac{2\pi}{3}) \end{bmatrix} \begin{bmatrix} i_{Sa} \\ i_{Sb} \\ i_{Sc} \end{bmatrix}$$

(5)

Where  $i_{Sa}$ ,  $i_{Sb}$ ,  $i_{Sc}$  are the ST three-phase currents.

As the  $v_{Sq}$  is zero, the ST powers can be obtained by (6) and (7), also the reference dqcomponent currents can be obtained by (8) and (9) [62]:

$$P_S = v_{Sd}.\,i_{Sd} \tag{6}$$

$$Q_S = -v_{Sd}.i_{Sq} \tag{7}$$

$$i_{Sq}^* = \frac{-Q_s^*}{v_{Sd}} \tag{8}$$

$$i_{Sd}^* = \frac{P_S^*}{v_{Sd}} \tag{9}$$

Where  $P_S$ ,  $Q_S$ ,  $i_{Sd}^*$ ,  $i_{Sq}^*$  are the active power, reactive power, and reference dq-component currents of the ST, respectively.

## 3.2.2. Control Of Receiving Terminal Converter

The Receiving Terminal (RT) converter mainly controls the reactive power and the DC link at the RT as shown in Figure 17. At the ST, the reference d-component current of ST  $i_{Sd}^*$  is generated by setting the reference active power. However, in the RT,  $i_{Rd}^*$  is regulated such that the DC voltage at the RT,  $V_{R,DC}$  matches a reference voltage  $V_{R,DC}^*$ . In this study, active power is transmitted at unity power factor thus  $i_{Sq}^*$  and  $i_{Rq}^*$  are set to zero by setting the reference reactive powers of both terminals to zero.

Figure 17: Receiving end control scheme

Following the same procedure to obtain the powers at the RT as given by (10) and (11), also the reference q-component current can be obtained by (8) and (9) as shown in (12) below:

$$P_R = v_{Rd}.i_{Rd} \tag{10}$$

$$Q_R = -\nu_{Rd}.i_{Rq} \tag{11}$$

$$i_{Sq}^* = \frac{-Q_R^*}{v_{Sd}}$$

(12)

where  $v_{Rd}$ ,  $i_{Rd}$ ,  $i_{Rq}$ ,  $P_R$ ,  $Q_R$ ,  $i_{Sq}^*$ ,  $Q_R^*$  are the d-component of the voltage, the d-component of the current, the q-component of the current, the active power, the reactive power of the RT, the reference q-component current of the ST and the reference reactive power of the RT, respectively. Finally, the adjusted dq components are transferred back to abc as in (13), in order to be fed to the PWM as reference signals to get the desired switching pattern.

$$\begin{bmatrix} v_a^* \\ v_b^* \\ v_c^* \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \sin(\theta) & \cos(\theta) \\ \sin(\theta - \frac{2\pi}{3}) & \cos(\theta - \frac{2\pi}{3}) \\ \sin(\theta + \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \end{bmatrix} \begin{bmatrix} v_d^* \\ v_q^* \end{bmatrix}$$

(13)

Where,  $v_a^*$ ,  $v_b^*$ ,  $v_c^*$  are the reference abc components used as modulation signals and  $v_d^*$ ,  $v_q^*$  are the reference dq-components of those modulation signals.

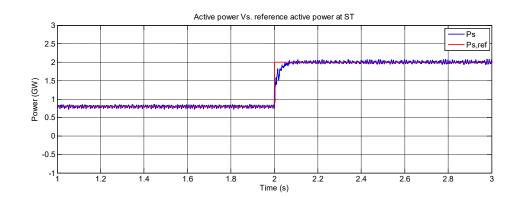

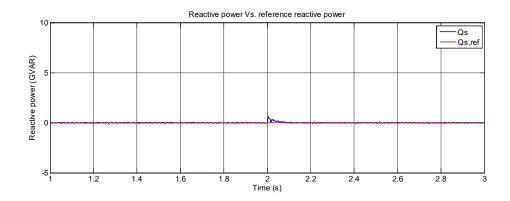

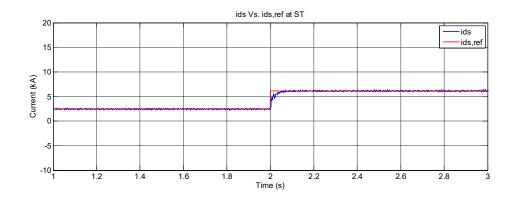

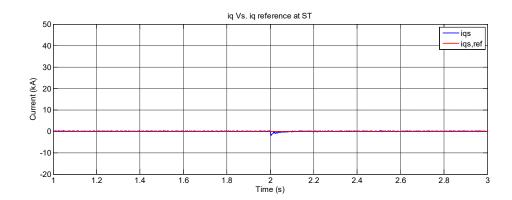

# 3.2.3. Simulation Results

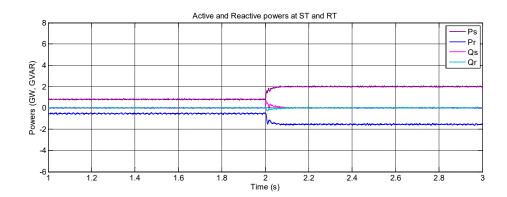

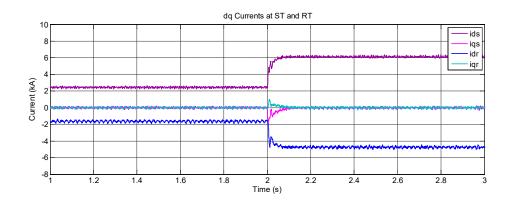

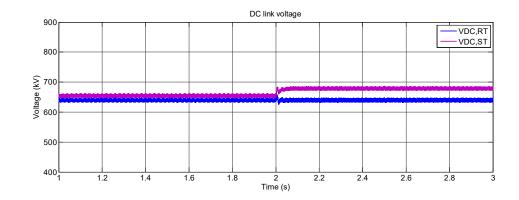

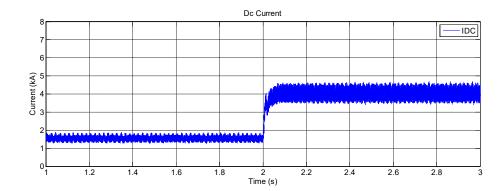

The two-terminal VSC-HVDC system has been modeled and simulated using MATLAB-Simulink platform. In this study, the LCL filter is designed based on (1) and (2) mentioned earlier in this chapter. As the switching frequency of the system is assumed 2 kHz, the corner frequency is located between the fundamental and the switching frequencies to avoid any resonance. Assuming that  $f_c = 250 \text{ Hz}$ , the values of  $L_f$  and  $C_f$  could be designed based on (1) as follows: Assume that  $C_f = 100\mu F$ , then  $L_f = 0.0634 \text{ mH}$ . Let  $L_{inv} = L_T = 8 \text{ mH}$  according to (2). The overall system's parameters referring to [62] are as presented in Table 1. In this study, active power is transmitted however, reactive power, is set to zero. Also, the DC link at the RT is regulated at a pre-determined reference value. Figure 18 and Figure 19 represent active and reactive powers respectively against their predetermined reference value. At steady state, the active power of the ST becomes equivalent to the reference value  $P_{ST}^*$ . In addition, Figure 20 and Figure 21 show the dq currents respectively versus their reference value. However, Figure 22 represents active and reactive powers of the ST and RT. The reactive power of both terminals is set to zero equivalent to the reference value. Figure 23 represents the dq currents of both ST and RT, where they perform similar to their corresponding power.

| Parameter                              | Value         |

|----------------------------------------|---------------|

| Grid Voltage (line-line)               | 400 kV        |

| Fundamental Frequency                  | 50 Hz         |

| Switching Frequency ( $f_s$ )          | 2 kHz         |

| DC Voltage                             | 640 kV        |

| AC Line Damping Resistance (R)         | 1 Ω           |

| LCL Filter Inductance $(L_g, L_{inv})$ | 8 mH          |

| LCL Filter Capacitance ( $C_f$ )       | $100 \ \mu F$ |

| High pass Filter Resistance $(R_f)$    | 0.01 Ω        |

| High pass Filter Inductance $(L_f)$    | 0.0634 mH     |

| DC Capacitance ( <b>C</b> )            | 94 µF         |

| DC Line Resistance                     | 0.0121 Ω/km   |

| DC Line Length                         | 400 km        |

| DCCB limiting reactor                  | 20 mH         |

Table 1: VSC-HVDC System's Parameter

The system is tested for the following case:

$$P_{S}^{*} = \begin{cases} 800 \ MW & 0 \le t < 2 \ s \\ 2 \ GW & 2 \le t \le 4 \ s \end{cases}$$

$$Q_{S}^{*} = Q_{R}^{*} = 0 \ \text{MVAR},$$

$$V_{R,DC}^{*} = 640 \ \text{kV}$$

Figure 18: Active power and reference active power at ST

Figure 19: Reactive power and reference reactive power at ST

Figure 20: d-component current and reference d-component current at ST

Figure 21: q-component current vs. reference q-component current at ST

Figure 22: Active and reactive powers of ST and RT

Figure 23: dq Currents of ST and RT

Figure 24: DC voltages of ST and RT

Figure 25: DC current

Figure 24, shows the DC voltages of the ST and RT. The DC voltage at RT is kept constant at the reference value while a slight change occurred at the ST DC link due to, the change in the reference power. Figure 25 represents the DC current through the DC transmission line from ST to RT. A step change is shown clearly in the DC current, that represents the change in the power flowing from ST to RT. Figure 26 and Figure 27 show the three-phase current and voltage at ST. In addition to, the three-phase current and voltage of RT shown in Figure 28 and Figure 29.

Figure 26: ST Three-phase grid side current of VSC-HVDC

Figure 27: ST Three-phase voltage of VSC-HVDC

Figure 28: RT Three-phase grid side current of VSC-HVDC

Figure 29: RT Three-Phase Voltage of VSC-HVDC

### 3.3. DC Side Fault

In VSC-HVDC transmission systems, DC side faults such as pole-to-pole and pole-toground faults, comprise major concern in the development of VSC-based DC networks [66]. Pole-to-pole DC fault is considered as a severe fault condition for VSC-HVDC systems regardless of the fault position along the DC cable. Generally, a pole-to-pole DC fault analysis can be described by the representation shown in Figure 30. Once the DC fault occurs, the fault current goes through the following steps [67]:

• **Capacitor discharge:** The DC link capacitors start to discharge rapidly. Hence the DC link voltage drops near to zero, where the natural response of the capacitor discharge current is known by its high peak and the exponential decay with time [67].

• **Diode freewheeling:** Once the capacitors discharge to a level less than the grid peak voltage, the switches are disabled, and the freewheeling diodes are forward biased as represented in Figure 30. The impedance of the cable drives the grid current into the DC fault passing through the freewheeling diodes path, in which the freewheeling diodes function as an uncontrolled rectifier feeding the DC fault. Each converter leg carries one-third of the fault current that may damage the diodes [67]

Figure 30: VSC-HVDC pole-to-pole fault schematic diagram

### 3.4. HVDC Systems Protection

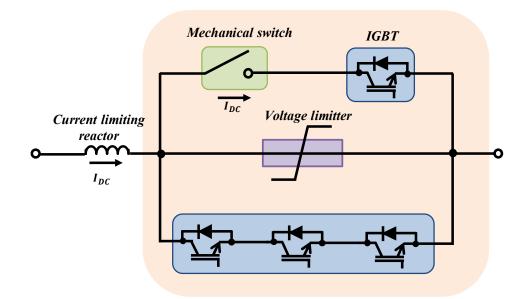

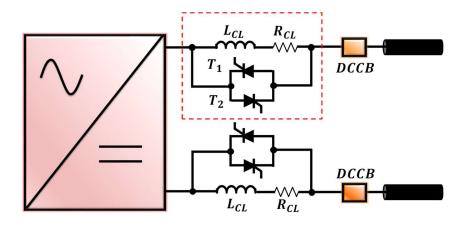

Currently, protection of point-to-point VSC-HVDC systems during fault at the DC side entail disconnection of the faulted line through AC circuit breakers and isolation of the whole DC system. However, this may not be a feasible option. Integrating HVDC Circuit Breakers (DCCB) may be another option [66], [67]. The clearance of the fault on such large systems, especially when more than two-terminals are connected should be fast enough to fulfill the requirements of a reliable HVDC system. Hence, existing mechanical HV DCCBs can clear the fault within several tens of milliseconds, but this is considered very slow. However, HV DCCBs based on semiconductor devices are fast enough to overcome the limitations of operating speed, but it generates higher losses. To overcome these problems, ABB has developed a hybrid DCCB that combines semiconductor switches and a mechanical switch as shown in Figure 31[69]. In normal operation mode, the current flows through the bypass branch which consists of the mechanical switch and the semiconductor switch (load commutation switch), while the current is zero in the main breaker [69]. When a fault occurs, the mechanical switch opens and hence, the current flows through the main breaker path to break the current [69]. The key features of this hybrid HV DCCB design are that it provides reduced conduction losses as there are no active semiconductor switches in the conduction path while maintaining fast current interruption capability [68], [69]. Also, the series-connected reactor is placed along with hybrid HV DCCB at the DC side in order to limit the fault current peak [68-70]. Large inductors with several hundreds of mH are deployed for the limitation of fault current, in which the peak and rising rate of fault current can be reduced within the breaking capability of DCCB [70]. However, large reactors cause overlap to the performance of the system controller and have a larger footprint as well as higher cost. Furthermore, the overvoltage limitation of the switching transients is not more than 1.4 times the nominal DC link voltage. Hence, it provides high reliability due to inherent redundant topology [71], [72].

Figure 31: Hybrid DC circuit breakers

To, better understand the system under DC side faults, the studied two-terminal two-level HVDC system has been subjected to a pole-to-pole permanent fault at the ST side as in Figure 32 in order to investigate the behavior of the VSC-HVDC. The fault has been applied at t=2 sec for two cases high and low fault resistance.

Figure 32: A pole-to-pole DC side fault at VSC-HVDC ST

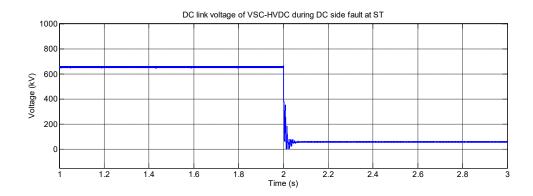

#### 3.4.1. Case 1: Low resistance Fault

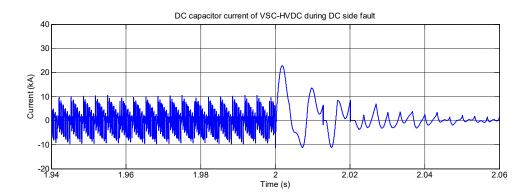

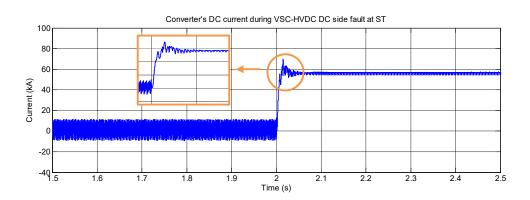

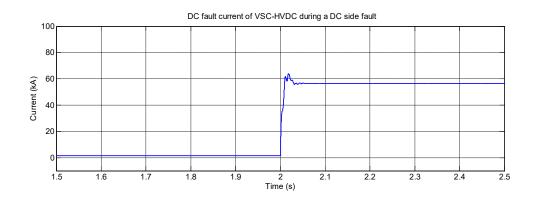

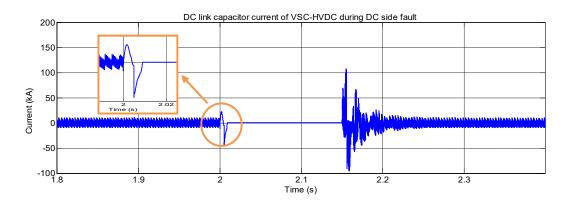

A pole-to-pole DC fault has been applied through R=0.5  $\Omega$  at t= 2 sec as in Figure 32. The results generated show that the DC link voltage of the ST drops near to zero as shown in Figure 33, DC capacitor starts to discharge high amplitude current as in Figure 34 according to the time constant of the elements as in (14):

$$\tau = RC \tag{14}$$

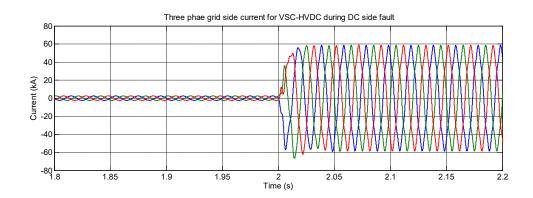

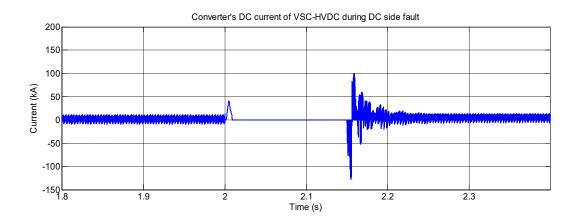

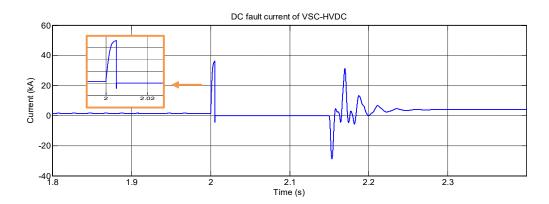

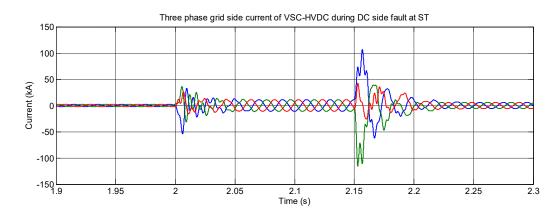

where, R represents the reactor and the fault resistance, and C represents the DC link capacitor. Also, VSC is subjected to high amplitude current passing through the freewheeling diodes as presented in Figure 35. In addition, to the high peak fault current shown in Figure 36. As well as, Figure 37 and Figure 38 represent the grid and converter side three-phase currents, respectively, during DC side fault at the ST, where the current in both sides have increased during the fault.

*Figure 33:* DC link voltage during fault t=2sec

Figure 34: DC capacitor current at DC side fault at t=2 sec

Figure 35: Inverter current during DC fault at t=2 sec

Figure 36: Fault current

*Figure 37*: Three-phase grid side current during DC fault at t=2sec.

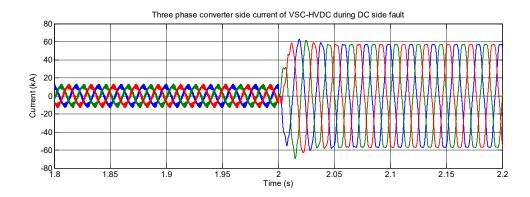

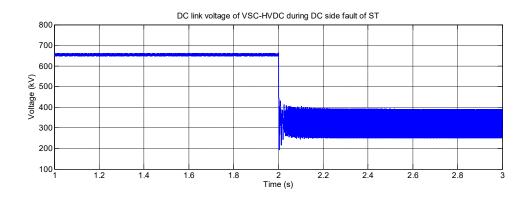

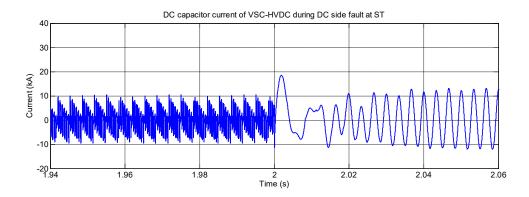

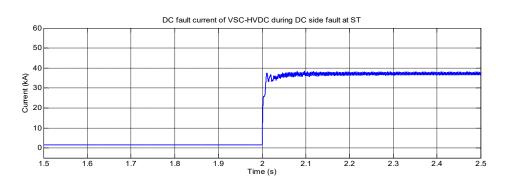

Figure 38: Three-phase converter side current of VSC-HVDC during DC side fault

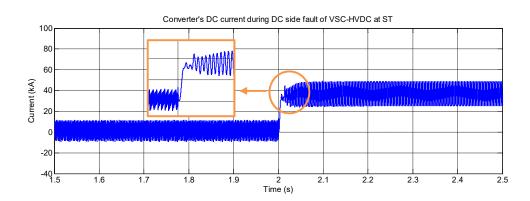

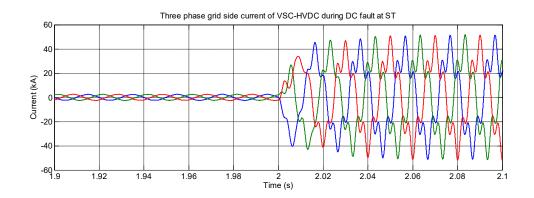

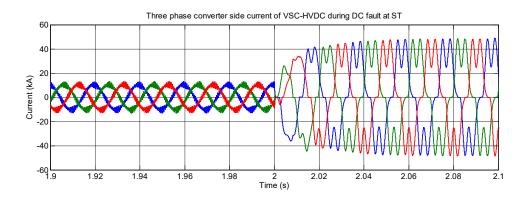

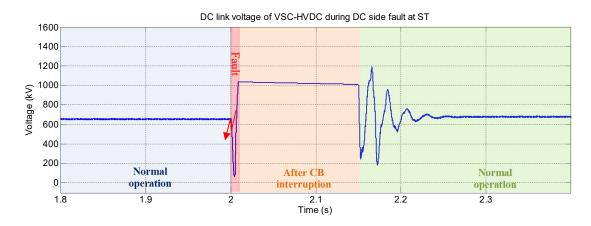

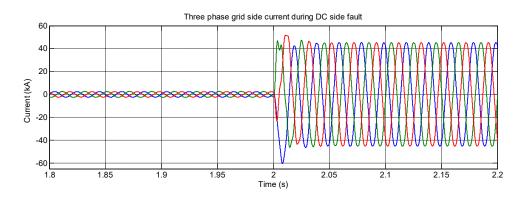

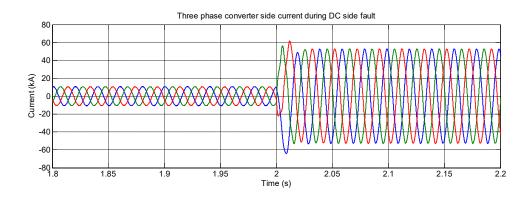

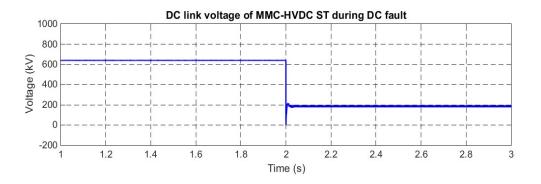

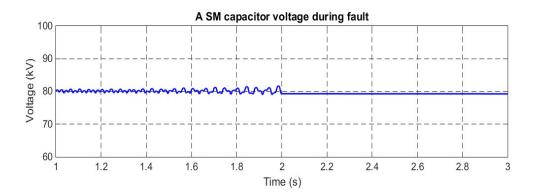

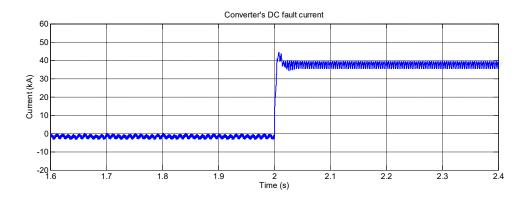

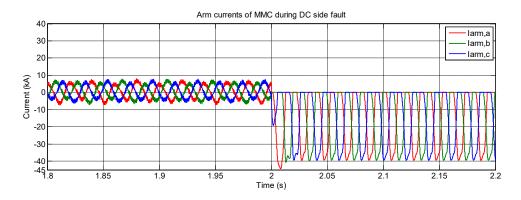

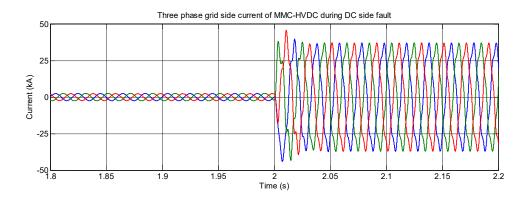

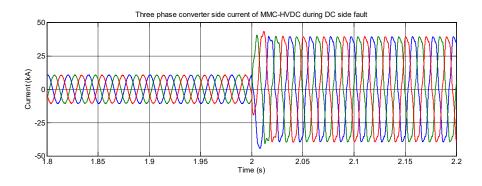

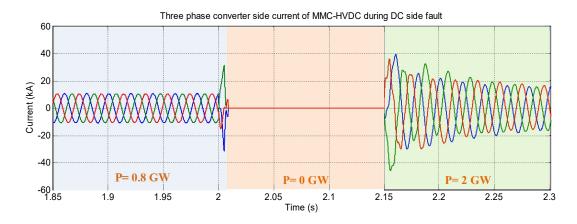

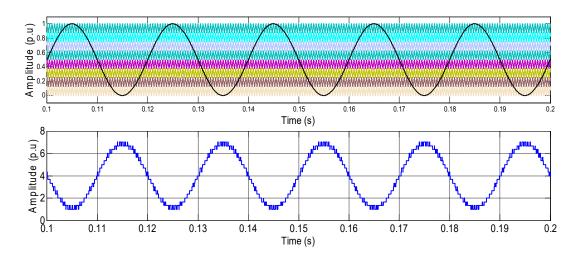

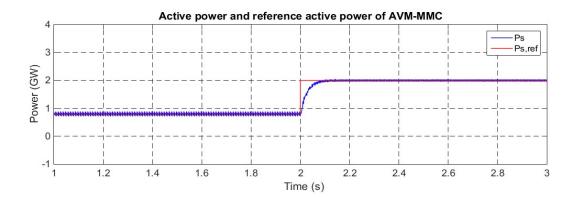

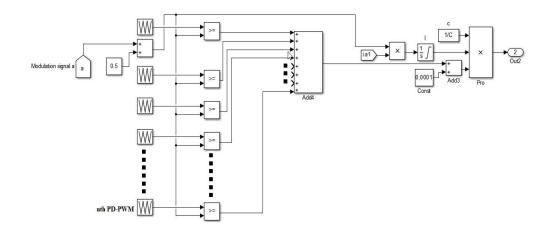

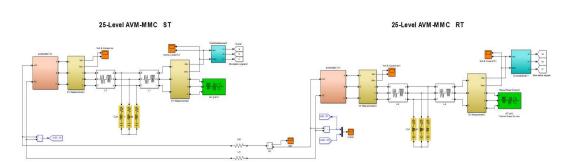

### 3.4.2. Case 2: High Resistance Fault