# IET Power Electronics

# Special issue Call for Papers

Be Seen. Be Cited. Submit your work to a new IET special issue

Connect with researchers and experts in your field and share knowledge.

Be part of the latest research trends, faster.

**Read more**

**IET Power Electronics**

### RAPID COMMUNICATION

# 11 Level boost inverter topology with dual-source configuration

Marif Daula Siddique<sup>1</sup> Mohammad Wasiq<sup>2</sup> Atif Iqbal<sup>1</sup> Saad Mekhilef<sup>3,4,5</sup> Addy Wahyudie<sup>6,7</sup> Muhyaddin Rawa<sup>4,8</sup>

<sup>1</sup>Department of Electrical Engineering, Qatar University, Doha, Qatar

<sup>2</sup>University of Roma II, Tor Vergata, Italy

<sup>3</sup>Department of Telecommunications, Electrical, Robotics and Biomedical Engineering, School of Software and Electrical Engineering, Swinburne University of Technology, Hawthorn, Victoria, Australia

<sup>4</sup>Smart Grids Research Group, Center of Research Excellence in Renewable Energy and Power Systems, King Abdulaziz University, Jeddah, Saudi Arabia

<sup>5</sup>Power Electronics and Renewable Energy Research Laboratory, Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia

<sup>6</sup>Department of Electrical and Communication Engineering, United Arab Emirates University, Al Ain, United Arab Emirates

<sup>7</sup>Water and Energy Center, United Arab Emirates University, Al Ain, United Arab Emirates

<sup>8</sup>Department of Electrical and Computer Engineering, Faculty of Engineering, K. A. CARE Energy Research and Innovation Center, King Abdulaziz University, Jeddah, Saudi Arabia

#### Correspondence

Saad Mekhilef, School of Science, Computing and Engineering Technologies, Swinburne University of Technology, Hawthorn, Victoria 3122, Australia. Email: smekhilef@swin.edu.au

#### Funding information

The authors acknowledge the support provided by King Abdullah City for Atomic and Renewable Energy (K.A.CARE) under K.A.CARE-King Abdulaziz University Collaboration Program. The Deanship of Scientific Research (DSR) at King Abdulaziz University, Jeddah, Saudi Arabia has funded this project, under grant no. (FP-108-43) and also the United Arab Emirates University (UAE-U) for supporting this research work through the AUA grants #12R022 and #31R280.

#### Abstract

With the advancement of the application of power converters in the power industry, the research towards the prominent power converter namely multilevel inverter has gained a lot of attraction. Here, a dual-source configured 11 level inverter topology is being discussed, which uses nine power semiconductor devices and one capacitor. The proposed topology is able to charge the capacitor up to  $2V_{d}$ , which provides the boosting feature with the voltage gain of 1.67. An extended comparison with several other topologies has been provided which highlights the major contribution of the work. A low-power laboratory prototype has been used for the validation of the proposed 11 level topology. Further, a thorough assessment of comparable topologies has been conferred in detail.

#### 1 **INTRODUCTION**

Multilevel inverters (MLIs) play a significant role in the development of EVs, HVDC, Fact devices renewable power plants, and microgrids. There are several prominent features of the MLIs inverter over two-level inverter, for example, low dv/dtcharacteristics, higher efficiency, superior EMC, modularity, and high fault tolerance abilities. However, the requirement of large number of dc sources, switches, diodes, capacitors, other components significantly rise the size and cost of the MLIs with higher voltage stress. A new approach toward the abovementioned problem has been discussed in this article which is based on the combinations of the component that have been introduced in different topologies of the MLIs [1, 2].

Several single source boost inverter topologies have been proposed, however, the required number of components has

been on the higher side. A developed switched-capacitor incorporated MLI with a string of dc sources is proposed in [3]. The main concern of the topology is to lower the stress at the backend H-bridge. The topology presented in [4] is based on switched capacitor producing seven-levels with self-voltage balancing at boosting factor of 3 without a backend H-bridge. In [5], an improved 7-level PUC inverter is investigated which uses a new voltage balancing method. The blocking voltage on the switches is low and the topology comes with boosting feature. The topology presented in [6] is a 19 level, three times voltage gain, hybrid switched-capacitor MLI which finds application in high-frequency ac distribution systems. This converter achieves self-voltage balancing by employing the series-parallel conversion method. MLI Topology suitable for high-frequency ac power distribution systems is developed in [7]. Under this, an asymmetric dc voltage source with a common ground is

This is an open access article under the terms of the Creative Commons Attribution-NonCommercial License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited and is not used for commercial purposes.

<sup>© 2022</sup> The Authors. IET Power Electronics published by John Wiley & Sons Ltd on behalf of The Institution of Engineering and Technology.

utilized to make it valuable for renewable energy farms and EVs. A 9-level PEC topology with reduced components count is presented in [8]. This topology enables multi-terminal operations and is suitable for both symmetrical and asymmetrical concoctions. In [9], a K-type modular multilevel inverter, in which capacitors are used as dc-link to produce 13-level staircase output waveform, is presented. A single-stage modified H-bridge SC-based seven-level multilevel inverter with triple voltage gain is presented in [10]. In [11], an improved sensor-less cascaded Ttype 9-level multilevel converter with a reduced switched count is presented. Another 9-level SC-based topology with reduced count is presented in [12]. The topology uses phase disposition PWM to improve the quality of the output waveform. Another high-frequency ac power distribution system application-based topology is investigated in [13]. The results demonstrate low THD without the utilization of a high-frequency modulation scheme.

A cascaded 7-level switched-capacitor with a single input source is investigated in [14]. Where the phase-shifted sinusoidal pulse width modulation scheme is considered to control the capacitor voltage. Further, for high-frequency application, a cascaded MLI based on the switched capacitor is developed in [15]. In which, the H-bridge at the backend and switched capacitor at the frontend are used to generate the output. A similar approach has been adopted in the topologies of [16–22], however, the device count has been the limiting factor for these topologies. In this work, a dual-source dc to ac converter topology has been presented. The two sources are configured in asymmetrical magnitudes with the integration of a switched capacitor unit to provide the boosting feature. The lower device count with lower voltage stress is the other advantage of the proposed topology.

# 2 | TOPOLOGICAL DESCRIPTION AND ANALYSIS

#### 2.1 | Proposed topology

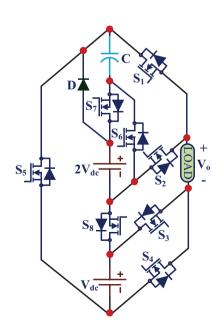

The proposed 11-level Inverter with voltage gain is demonstrated in Figure 1. The major component of the proposed MLI are:

- · Eight unidirectional switches

- · Two dc sources in asymmetrical magnitude

- One diode

- One capacitor

The output voltage waveform is an 11-level across the load with the voltage level of  $\pm V_{dc}$ ,  $\pm 2V_{dc}$ ,  $\pm 3V_{dc}$ ,  $\pm 4V_{dc}$ ,  $\pm 5V_{dc}$ . The proposed topology has four pairs of complementary switches (S<sub>1</sub>, S<sub>2</sub>), (S<sub>3</sub>, S<sub>4</sub>), (S<sub>6</sub>, S<sub>7</sub>), (S<sub>5</sub>, S<sub>8</sub>). To prevent short-circuit conditions, the switches must not be turned ON simultaneously.

#### 2.2 | Description of voltage states

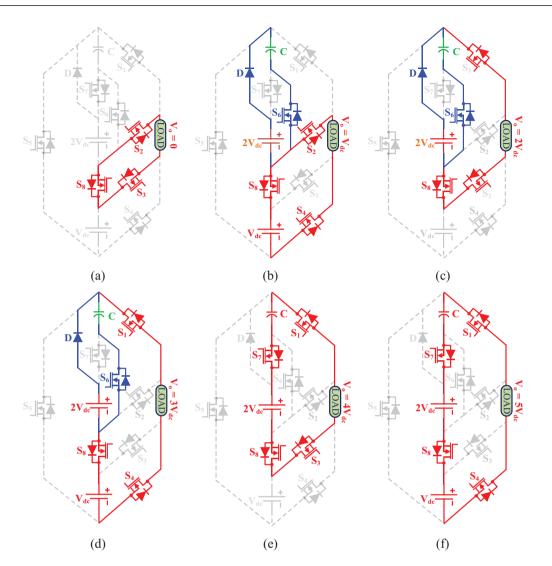

The voltage levels produced by the proposed topology have been shown in Figure 2a-f for the positive half cycle and is discussed below:

# 2.2.1 | Zero voltage state ( $V_o = 0$ )

With zero output voltage level in this state, only three switches are conducting for producing this state as shown in Figure 2a. For this state, there is no cycle of charging and discharging happens for the capacitor  $C_1$ .

### 2.2.2 | First voltage state ( $V_o = V_{dc}$ )

The capacitor C starts charging from  $2V_{dc}$  source in this state as shown in Figure 2b. The current flows through  $S_2$ ,  $S_4$ ,  $S_6$ ,  $S_8$ . The output voltage level for this state is  $V_{dc}$ .

2.2.3 | Second voltage state (

$$V_{a} = 2V_{dc}$$

)

In this state, the capacitor C still charges from  $2V_{dc}$  and the output voltage is obtained from the same source  $2V_{dc}$  as shown in Figure 2c. The current flows from the path from S<sub>1</sub>, load, S<sub>3</sub>, S<sub>8</sub>,  $2V_{dc}$ , diode D. The output voltage level generated in this state is  $2V_{dc}$ .

2.2.4 | Third voltage state  $(V_a = 3V_{da})$

The state can be obtained by following the current path  $S_1$ ,  $S_4$ ,  $V_{dc}$ ,  $S_8$ ,  $2V_{dc}$ , Diode D and is shown in Figure 2d. The output voltage level achieved in this state is  $3V_{DC}$ . The capacitor is still charging from the source  $2V_{dc}$  by following path  $2V_{dc}$ , D, capacitor C,  $S_6$ .

2.2.5 | Fourth voltage state ( $V_{a} = 4V_{da}$ )

From this state as shown in Figure 2e, the capacitor C starts discharging. The current follows the path  $S_1$ , load,  $S_8$ ,  $2V_{dc}$ ,  $S_7$ , C. The output voltage level obtained from this state is  $4V_{dc}$ .

FIGURE 1 Proposed 11 level topology

17554543.0, Downloaded from https://ietresearch.onlinelibrary.wiley.com/doi/10.1049/pel2.12317 by Qatar University, Wiley Online Library on [21/05/2023]. See the Term:

and Condit

(https:/

ibrary.wiley

and

conditions) on Wiley Online Library for rules

of use; OA articles are governed by the applicable Creative Commons License

**FIGURE 2** Positive voltage states of the proposed 11 level topology with (a)  $V_{\theta} = 0$ , (b)  $V_{\theta} = V_{de}$ , (c)  $V_{\theta} = 2V_{de}$ , (d)  $V_{\theta} = 3V_{de}$ , (e)  $V_{0} = 4V_{de}$ , (f)  $V_{\theta} = 5V_{de}$

# 2.2.6 | Fifth voltage state ( $V_{o} = 5 V_{dc}$ )

This is the last state for the positive output staircase waveform and is as shown in Figure 2f. In this state, the output voltage level of  $5V_{dc}$  can be obtained by following the path S<sub>1</sub>, load, S<sub>4</sub>,  $V_{dc}$ , S<sub>8</sub>,  $2V_{dc}$ , S<sub>7</sub>, C.

Similarly, the negative voltage levels can be obtained conferring to Table 1 which demonstrates the switching combinations for the proposed topology with both for the positive and negative voltage levels along with the voltage behaviour of the capacitor *C*.

#### 2.3 | Capacitance value calculation

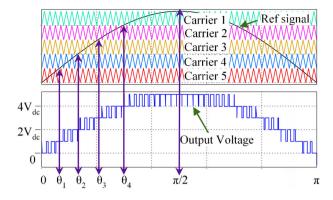

The role of the capacitance value of capacitor C is very crucial in order to satisfice the higher standards of performance. Figure 3 shows the arrangement of carrier signals with the reference along with the output voltage. The capacitor is charged

TABLE 1 Switching sequence of the proposed 11 level circuit

|                       |                       | 0 110          | ining see             | quenee o | n une pro             | posed I               | 1 10 001 01    | reur      |          |

|-----------------------|-----------------------|----------------|-----------------------|----------|-----------------------|-----------------------|----------------|-----------|----------|

| <b>S</b> <sub>1</sub> | <b>S</b> <sub>2</sub> | S <sub>3</sub> | <b>S</b> <sub>4</sub> | $S_5$    | <b>S</b> <sub>6</sub> | <b>S</b> <sub>7</sub> | S <sub>8</sub> | $V_o$     | $V_C$    |

| 0                     | 1                     | 1              | 0                     | 0        | 0                     | 0                     | 1              | Zero      | -        |

| 0                     | 1                     | 0              | 1                     | 0        | 1                     | 0                     | 1              | $V_{dc}$  | $C_{ch}$ |

| 1                     | 0                     | 1              | 0                     | 0        | 1                     | 0                     | 1              | $2V_{dc}$ | $C_{ch}$ |

| 1                     | 0                     | 0              | 1                     | 0        | 1                     | 0                     | 1              | $3V_{dc}$ | $C_{ch}$ |

| 1                     | 0                     | 1              | 0                     | 0        | 0                     | 1                     | 1              | $4V_{dc}$ | $D_{ch}$ |

| 1                     | 0                     | 0              | 1                     | 0        | 0                     | 1                     | 1              | $5V_{dc}$ | $D_{ch}$ |

| 1                     | 0                     | 0              | 1                     | 1        | 0                     | 0                     | 0              | Zero      | _        |

| 1                     | 0                     | 1              | 0                     | 1        | 1                     | 0                     | 0              | $V_{dc}$  | $C_{ch}$ |

| 0                     | 1                     | 0              | 1                     | 1        | 1                     | 0                     | 0              | $2V_{dc}$ | $C_{ch}$ |

| 0                     | 1                     | 1              | 0                     | 1        | 1                     | 0                     | 0              | $3V_{dc}$ | $C_{ch}$ |

| 0                     | 1                     | 0              | 1                     | 1        | 0                     | 1                     | 0              | $4V_{dc}$ | $D_{ch}$ |

| 0                     | 1                     | 1              | 0                     | 1        | 0                     | 1                     | 0              | $5V_{dc}$ | $D_{ch}$ |

|                       |                       |                |                       |          |                       |                       |                |           |          |

Notation: 0 = Not conducting, 1 = Conducting, Capacitor voltage state with - = no change,  $C_{ch} = Charging, D_{ch} = Discharging,$

**FIGURE 3** 11 level waveform with the arrangement of carriers and references

during the  $\pm V_{dc}$ ,  $\pm 2V_{dc}$ ,  $\pm 3V_{dc}$  voltage levels and discharged at the voltage levels of  $\pm 4V_{dc}$  and  $\pm 5V_{dc}$ . As the capacitors are discharged during the voltage states during  $\pm 4V_{dc}$  and  $\pm 5V_{dc}$ , the maximum discharge time constitutes from  $\pi - 2\theta_3$ . As the charging and discharging of the capacitor is symmetrical, it shows the self-balancing behaviour of the voltage of the capacitor with some ripple content in its voltage which is dependent on various factors as given in (1).

$$C_{value} = \frac{5V_{de}}{2\pi \times f_o \times R \times \Delta V_C} \times (\pi - 2\theta_3)$$

(1)

where  $C_{value}$ ,  $f_o$ , R, and  $\Delta V_C$  denotes the capacitance value, output voltage frequency, load resistance, ripple voltage, and maximum discharge time, respectively.

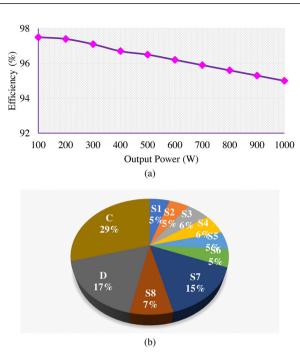

#### 2.4 | Analysis of power loss

The analysis related to the power loss of the proposed 11-level MLI has been carried out using PLECS software. Two main losses in the switched capacitor based MLI are the losses linked with power devices and capacitors losses. The power semiconductor losses are mainly dependent on the voltage across the device, the current flowing through it, the operating frequency whereas the power loss of capacitor depends on its equivalent series resistance (ESR), current flow through it, the ripple content in its voltage. With PLECS, the thermal model of the proposed dual-source topology using the data from the manufacturer datasheet of switch IKW75N60T has been used. The magnitude of the voltage sources has been selected as 50 and 100 V which results in a peak output voltage of 250 V. The load parameters have changed to get the efficiency at different output power. The estimated efficiency has been depicted in Figure 4a. Further, the loss distribution among the components of the proposed topology has been provided in Figure 4b. As expected, the devices in the charging loop of capacitor C have a maximum percentage due to losses associated with the charging current.

#### 3 | COMPARATIVE STUDY

To demonstrate the feature discussed in the previous section, a comparative analysis is performed in this section against some

FIGURE 4 (a) Efficiency curve and (b) loss distribution

of the recent topologies [4, 5, 10, 16-22]. The comparison is done on the basis of the available number of switches, number of diodes, number of capacitors, voltage gain, TSV, and PIV. Table 2 gives the detail of the topologies in terms of comparative parameters. From Table 2, it is clear that the topologies [4, 5, 10] require less dc sources, but, to generate lower number of levels higher number of switches are needed. In case of [17, 18, 20], there is no need of a capacitor to produce the staircase output but they require higher number of dc sources as compared to the proposed topology. The topology presented in [16, 19] produces the same level of output but requires more and diode in comparison to the proposed topology. In case of MLIs elaborated in [21, 22], using less dc sources and requires no diode, however, to produce output voltage of 11-level the required switches as well as capacitance are much more than the proposed MLI.

In the topologies [4, 10, 19], the gain is higher with the same number of dc sources as compared to the proposed topology at the cost of higher number of capacitors and the number of switches. The topology presented in [5] has same gain, capacitances and dc sources but produces lower level with higher switch count. The rest of the topologies have lower voltage gain with higher number of components in comparison to the proposed topologies.

In comparison Table 2, a cost comparison is shown to analyze the cost of the topologies. The Cost Factor is calculated as:

$$CF = \left(N_s + N_D + N_{Cap} + N_{DC} + TSV_{PU} \times \sigma\right) / N_L \quad (2)$$

From Table 2, the cost factor is the lowest for the proposed topology. This also shows the merit of the proposed topology.

TABLE 2 Comparison of SC based MLI topology

|      |    |       |       | N <sub>Cap</sub> | N <sub>DC</sub> | G   | $TSV_{PU}$ | $N_S/N$ | N <sub>CD(h)</sub> | Cost factor    |                |

|------|----|-------|-------|------------------|-----------------|-----|------------|---------|--------------------|----------------|----------------|

| Тор  | N  | $N_S$ | $N_D$ |                  |                 |     |            |         |                    | $\sigma = 0.5$ | $\sigma = 1.0$ |

| [4]  | 7  | 12    | 0     | 2                | 1               | 3   | 5.3        | 1.71    | 10                 | 2.52           | 2.9            |

| [5]  | 7  | 9     | 0     | 1                | 1               | 1.5 | 1          | 1.28    | 4                  | 1.64           | 1.71           |

| [10] | 7  | 16    | 0     | 2                | 1               | 3   | 1          | 2.28    | 4                  | 2.78           | 2.85           |

| [16] | 11 | 20    | 18    | 10               | 1               | 1   | NS         | 1.82    | 6                  | NS             | NS             |

| [17] | 11 | 9     | 5     | 0                | 5               | 1   | 4          | 0.81    | 6                  | 1.90           | 2.09           |

| [18] | 11 | 8     | 3     | 0                | 3               | 1   | NS         | 0.72    | 2                  | NS             | NS             |

| [19] | 11 | 14    | 0     | 4                | 1               | 5   | 2.29       | 1.27    | 6                  | 1.83           | 1.93           |

| [20] | 11 | 12    | 0     | 0                | 6               | 1   | 2          | 1.09    | 5                  | 1.72           | 1.81           |

| [21] | 11 | 12    | 0     | 5                | 1               | 1   | 3          | 1.09    | 5                  | 1.77           | 1.90           |

| [22] | 11 | 11    | 0     | 2                | 1               | 1   | 3          | 1.00    | 5                  | 1.40           | 1.54           |

| [P]  | 11 | 8     | 1     | 1                | 2               | 1.5 | 1.4        | 0.72    | 4                  | 1.15           | 1.21           |

N–Number of levels, N<sub>5</sub>–Number of switches, N<sub>D</sub>–Number of diodes, N<sub>aap</sub>–Number of capacitors, N<sub>DC</sub>–Number of dc source, G–voltage gain, TSV<sub>PU</sub>–Per unit total standing voltage, NS – Not specified, N<sub>CD/0</sub>–Number of components conducted at the highest level.

TABLE 3 Parameters of the topology

| Parameters            | Values                                   |  |  |  |  |

|-----------------------|------------------------------------------|--|--|--|--|

| Input DC voltage      | 50 V, 100 V                              |  |  |  |  |

| Output peak voltage   | 250 V                                    |  |  |  |  |

| Fundamental frequency | 50 Hz                                    |  |  |  |  |

| Switching frequency   | 5 kHz                                    |  |  |  |  |

| L load                | 50 mH                                    |  |  |  |  |

| Capacitor             | $2200 \mu\text{F}$                       |  |  |  |  |

| R-load                | 50 <b>Ω</b> , 75 <b>Ω</b> , 100 <b>Ω</b> |  |  |  |  |

## 4 | RESULTS AND DISCUSSION

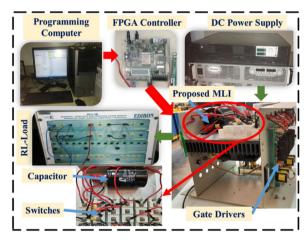

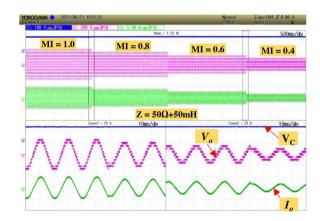

The validation of the proposed converter is evaluated based on experiments conducted on the experimental setup. The MLI requires control signals to fire the gates of the switches. To achieve this, many modulation schemes have been used. One of them is SPWM, that is, sinusoidal pulse width modulation. There are two types of sinusoidal PWM multiple carrier arrangements that provide the necessary gate pulse to the switches in the MLI: sinusoidal pulse width modulation with Level-shifted carriers (SPWM-LS) and sinusoidal pulse width modulation with phase-shifted carriers (SPWM-PS). In this study, an SPWM- LS is employed for the proposed 11 level inverter and the carriers are arranged as displayed in Figure 3. The five triangular carrier signals with 5 kHz frequency are disposed and the gating pulses are produced. Table 3 gives the value of different used components. The experimental prototype setup is depicted in Figure 5.

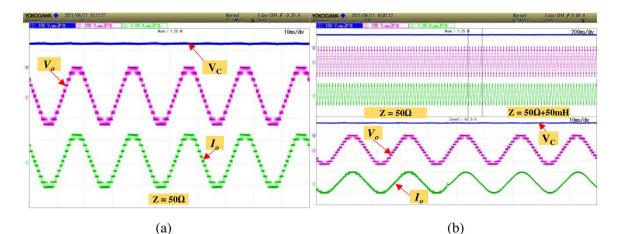

The waveform presented in Figure 6 demonstrates the analysis of the proposed 11 level topology. Figure 6a presents the output voltage and output current for the 11 level topology. The variation in the nature of the load is shown in Figure 6b, where

FIGURE 5 Hardware prototype of the proposed topology

the load changes from R-load to RL-load, that is, from a unity power factor to a lagging power factor of 0.95. From Figure 6b, it can be observed that there is no variation in the voltage when the load changes from R-load to RL-load, however, the current smoothens. Figures 6c and d show the loading condition for different R-load and RL-load. In Figure 6c, the load power factor is unity in all the changes in load whereas in Figure 6d, the power factor changes from 0.99 to 0.95 and again to 0.95. As the overall load impedance increases, the current decreases, vice versa can also be observed.

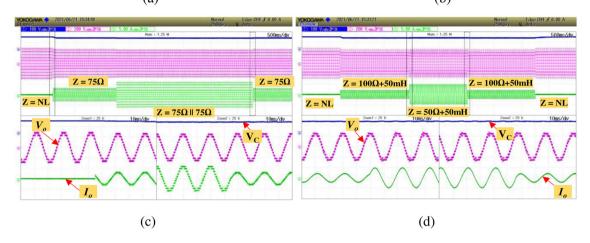

Figure 7 shows the deviation of voltage level as the modulation index (MI) varies. The level decreases as the modulation index decrease, that is, five-level at MI = 0.40, seven-levels at MI = 0.60, nine-levels at MI = 0.80, 11 levels at MI = 1.0. From all these waveforms, the self-balancing of the capacitor voltage is confirmed. In addition, the proposed topology provides excellent performance in different loading conditions.

**FIGURE 6** Waveform for output voltage  $(V_0)$ , capacitor voltage  $(V_C)$  and output current  $(I_0)$ . (a,b) Variation of load from R-load to RL-load, (c) variation of R-load, (d) variation of RL-load

FIGURE 7 Experimental results with the change in MI

### 5 | CONCLUSION

This study presents an 11L MLI with the reduction in the switch count, with higher boosting capability having a dual-source configuration. It combines eight switches, one capacitor, one diode. A detailed comparative analysis is performed to prove the superiority of the proposed MLI in association with the recent converters. The major contribution of the proposed topology is a lower device count as compared to recent topologies. In addition, the proposed topology has the prominent feature of higher efficiency and sensorless balancing of the capacitor voltage. The validation of the proposed 11 levels MLI is performed under diverse operating environments with the help of a developed experimental prototype.

#### ACKNOWLEDGMENT

The authors acknowledge the support provided by King Abdullah City for Atomic and Renewable Energy (K.A.CARE) under K.A.CARE-King Abdulaziz University Collaboration Program. The Deanship of Scientific Research (DSR) at King Abdulaziz University, Jeddah, Saudi Arabia has funded this project, under grant no. (FP-108-43) and also the United Arab Emirates University (UAE-U) for supporting this research work through the AUA grants #12R022 and #31R280.

#### CONFLICT OF INTEREST

There is no conflict of interest.

#### DATA AVAILABILITY STATEMENT

Data sharing not applicable – no new data generated, or the article describes entirely theoretical research.

#### ORCID

*Marif Daula Siddique* https://orcid.org/0000-0002-0799-500X

Atif Iqbal<sup>D</sup> https://orcid.org/0000-0002-6932-4367

#### REFERENCES

- Jayabalan, M., Jeevarathinam, B., Sandirasegarane, T.: Reduced switch count pulse width modulated multilevel inverter. IET Power Electron. 10(1), 10–17 (2017). https://doi.org/10.1049/iet-pel.2015.0720

- Khenar, M., Taghvaie, A., Adabi, J., Rezanejad, M.: Multi-level inverter with combined T-type and cross-connected modules. IET Power Electron. 11(8), 1407–1415 (2018). https://doi.org/10.1049/iet-pel.2017.0378

- Lee, S.S., Lee, K.B., Alsofyani, I.M., Bak, Y., Wong, J.F.: Improved switched-capacitor integrated multilevel inverter with a DC source string. IEEE Trans. Ind. Appl. 55(6), 7368–7376 (2019). https://doi.org/10. 1109/TIA.2019.2893850

- Siddique, M.D., Mekhilef, S., Shah, N.M., Ali, J.S.M., Blaabjerg, F.: A new switched capacitor 7L inverter with triple voltage gain and low voltage stress. IEEE Trans. Circuits Syst. II Express Briefs 67(7), 1294–1298 (2020). https://doi.org/10.1109/TCSII.2019.2932480

- Sathik, M.J., Bhatnagar, K., Sandeep, N., Blaabjerg, F.: An Improved Seven-Level PUC Inverter Topology with Voltage Boosting. IEEE Trans. Circuits Syst. II Express Briefs 67(1), 127–131 (2020). https://doi.org/10.1109/ TCSII.2019.2902908

- Fong, Y.C., Raman, S.R., Ye, Y., Cheng, K.W.E.: Generalized topology of a hybrid switched-capacitor multilevel inverter for high-frequency AC power distribution. IEEE J. Emerging Sel. Top. Power Electron. 8(3), 2886–2897 (2020). https://doi.org/10.1109/JESTPE.2019.2905421

- Raman, S.R., Fong, Y.C., Ye, Y., Eric Cheng, K.W.: Family of multiport switched-capacitor multilevel inverters for high-frequency AC power distribution. IEEE Trans. Power Electron. 34(5), 4407–4422 (2019). https:// doi.org/10.1109/tpel.2018.2859030

- Sharifzadeh, M., Al-Haddad, K.: Packed E-cell (PEC) converter topology operation and experimental validation. IEEE Access 7, 93049–93061 (2019). https://doi.org/10.1109/ACCESS.2019.2924009

- Samadaei, E., Kaviani, M., Bertilsson, K.: A 13-levels module (K-Type) with two DC sources for multilevel inverters. IEEE Trans. Ind. Electron. 66(7), 5186–5196 (2019). https://doi.org/10.1109/TIE.2018.2868325

- Lee, S.S.: A single-phase single-source 7-level inverter with triple voltage boosting gain. IEEE Access 6, 30005–30011 (2018). https://doi.org/10. 1109/ACCESS.2018.2842182

- Sandeep, N., Yaragatti, U.R.: A switched-capacitor-based multilevel inverter topology with reduced components. IEEE Trans. Power Electron. 33(7), 5538–5542 (2018). https://doi.org/10.1109/TPEL.2017.2779822

- Ngo, B.B., Nguyen, M.K., Kim, J.H., Zare, F.: Single-phase multilevel inverter based on switched-capacitor structure. IET Power Electron. 11(11), 1–8 (2018). https://doi.org/10.1049/iet-pel.2017.0857

- 13. Liu, J., Wu, J., Zeng, J., Guo, H.: A novel nine-level inverter employing one voltage source and reduced components as high-frequency ac power

source. IEEE Trans. Power Electron. 32(4), 2939–2947 (2017). https://doi.org/10.1109/TPEL.2016.2582206

- Sun, X., Wang, B., Zhou, Y., Wang, W., Du, H., Lu, Z.: A single DC source cascaded seven-level inverter integrating switched-capacitor techniques. IEEE Trans. Ind. Electron. 63(11), 7184–7194 (2016). https://doi. org/10.1109/TIE.2016.2557317

- Liu, J., Cheng, K.W.E., Ye, Y.: A cascaded multilevel inverter based on switched-capacitor for high-frequency AC power distribution system. IEEE Trans. Power Electron. 29(8), 4219–4230 (2014). https://doi.org/ 10.1109/TPEL.2013.2291514

- Widyo Astomo, R.B., Ashari, M.: Soedibyo: A design of diode-clamped 11-level inverter and its harmonic effect on transformer losses. In: 2020 International Seminar on Intelligent Technology and Its Applications (ISI-TIA), Surabaya, Indonesia (2020). https://doi.org/10.1109/isitia49792. 2020.9163696

- Cahyosaputro, W.A., Heru, L.: A single phase 11-level inverter for photovoltaic application. In: 2018 5th International Conference on Information Technology, Computer, Electrical Engineering (ICITACEE), Semarang, Indonesia (2018). https://doi.org/10.1109/icitacee.2018.8576947

- Tjokro, C., Pratomo, L.H.: Design and simulation of an asymmetrical 11-level inverter for photovoltaic applications. In: 2018 5th International Conference on Information Technology, Computer, Electrical Engineering (ICI-TACEE), Semarang, Indonesia (2018). https://doi.org/10.1109/icitacee. 2018.8576943

- Karimi, M., Kargar, P., Varesi, K.: A novel high-gain switched-capacitor based 11-level inverter topology. In: 2019 International Power System Conference (PSC), Tehran, Iran (2019). https://doi.org/10.1109/psc49016.2019. 9081558

- Girish Ganesan, R., Bhaskar, M., Narayanan, K.: Novel 11-level multi-level inverter. In: 2018 IEEE Innovative Smart Grid Technologies - Asia (ISGT Asia), Singapore (2018) https://doi.org/10.1109/isgt-asia.2018.8467799

- Panda, N., Das, B., Chakrabarti, A., Kasari, P.R., Bhattacharya, A., Chatterjee, D.: a new grid interactive 11-level hybrid inverter topology for medium-voltage application. IEEE Trans. Ind. Appl. 57(1), 869–881 (2021). https://doi.org/10.1109/tia.2020.3040204

- Ali, M., Tariq, M., Chakrabortty, R.K., Ryan, M.J., Alamri, B., Bou-Rabee, M.A.: 11-level operation with voltage-balance control of WE-type inverter using conventional and DE-SHE techniques. IEEE Access 9, 64317–64330 (2021). https://doi.org/10.1109/access.2021.3072905

How to cite this article: Siddique, M.D., Wasiq, M., Iqbal, A., Mekhilef, S., Wahyudie, A., Rawa, M.: 11 Level boost inverter topology with dual-source configuration. IET Power Electron. 1–7 (2022). https://doi.org/10.1049/pel2.12317

.