Received February 1, 2022, accepted February 18, 2022, date of publication February 22, 2022, date of current version March 8, 2022. *Digital Object Identifier* 10.1109/ACCESS.2022.3153510

# Modeling and Control of Single-Stage Quadratic-Boost Split Source Inverters

SHERIF M. DABOUR<sup>®1,2</sup>, (Senior Member, IEEE), MAJED A. ALOTAIBI<sup>®3</sup>, (Member, IEEE), AMR A. ABD-ELAZIZ<sup>®1</sup>, MAHMOUD A. ALSHAHAT<sup>1</sup>, (Student Member, IEEE), MAHMOUD ABDALLAH<sup>4</sup>, (Senior Member, IEEE), ALI M. ELTAMALY<sup>®5</sup>, AYMAN S. ABDEL-KHALIK<sup>®6</sup>, (Senior Member, IEEE),

AHMED M. MASSOUD<sup>®7</sup>, (Senior Member, IEEE), AND SHEHAB AHMED<sup>®8</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical Power and Machines Engineering, Tanta University, Tanta 31733, Egypt

<sup>2</sup>Electrical Power Engineering Department, School of Engineering and Built Environment, Glasgow Caledonian University, Glasgow G4 0BA, U.K.

<sup>3</sup>Department of Electrical Engineering, King Saud University, Riyadh 11421, Saudi Arabia

- <sup>5</sup>Sustainable Energy Center, King-Saud University, Riyadh 11421, Saudi Arabia

- <sup>6</sup>Department of Electrical Engineering, Alexandria University, Alexandria 21544, Egypt

- <sup>7</sup>Department of Electrical Engineering, Qatar University, Doha, Qatar

- <sup>8</sup>Department of Electrical Engineering, KAUST, Thuwal 23955, Saudi Arabia

Corresponding author: Majed Alotaibi (majedalotaibi@ksu.edu.sa)

This work was supported by the Deanship of Scientific Research at King Saud University through Research Group, Saudi Arabia, under Grant RG-1441-422.

**ABSTRACT** This paper aims to develop the recently introduced Spilt-Source Inverter (SSI) topology to improve its boosting characteristics. New SSI topologies with high voltage gain are introduced in this paper. The proposed converters square the basic SSI's boosting factor by utilizing an additional inductor, capacitor, and two diodes. Thus, the proposed converters are called Quadratic-Boost (or Square-Boost) SSIs (QBIs or SBIs). Four different OBI topologies are presented. One with continuous input current (CC-OBI), and the other draws a discontinuous input current (DC-QBI) but with reduced capacitor voltage stresses. This paper also introduces the small-signal model of the CC-QBI using state variables perturbance. Based on this model, the closed-loop voltage and current control approach of the dc-boosting factor are designed. Moreover, a modified space vector modulation (MSVM) scheme is presented to reduce the input current ripples. To evaluate the performance of the proposed topologies, a comparative study between them and the other counterpart from different perspectives is introduced. It can be found that the CC-QBI topology has superior boosting characteristics when operating with low input voltage compared with their counterparts. It has a higher boosting capability, lower capacitor voltages, and semiconductor stresses, especially when high voltage gains are required. These merits make the proposed topologies convenient to the Photovoltaic and Fuel-Cell systems. Finally, the feasibility of the suggested topology and the introduced mathematical model is verified via simulation and experimental results, which show good accordance with the theoretical analysis.

**INDEX TERMS** Split-source inverters (SSI), quasi-z source inverters, dc-ac boost converter, space-vector PWM.

#### I. INTRODUCTION

Renewable Energy Sources (RES) have been rapidly growing in the past two decades to solve conventional power plants' problems and thus overwhelmed their negative impacts on the environment. Among RES, the Photovoltaic (PV) and

The associate editor coordinating the review of this manuscript and approving it for publication was Ton Duc  $Do^{\textcircled{D}}$ .

fuel cell (FC) technologies are cleaner, and their penetration into the power system is continuously increasing [1], [2]. This growth has triggered the evolution of the dc-ac boost converter technologies, which are essential for interfacing the low voltage PV and FC modules (e.g., 20-40 Vdc) with the higher voltage grid or supplying isolated loads (e.g., 200-400 Vac) [3]–[5]. For this reason, the dc-ac boost converters undeniably represent an urgent research topic of

<sup>&</sup>lt;sup>4</sup>Department of Electrical Power and Machines Engineering, Faculty of Engineering, South Valley University, Qena 83523, Egypt

continuously gaining interest in power electronics [6]. The possible solution to realize dc-ac conversions with high gains are classified into two-stage and single-stage converters.

The two-stage dc-ac converter has traditionally been used as the standard solution to interface RES with the loads/grids. In this topology, a dc-dc boost converter with high voltage gain is required to boost the low voltage of PV or FC panels [6]. After that, the Voltage Source Inverter (VSI) is used in the inversion process. There are two main types of dc-dc converters, namely isolated and non-isolated configurations [7]. In both, high voltage gains generally can be obtained using switched impedance (inductance and capacitance), voltage boost cells, cascading architecture, and coupled inductor [8]. Admittedly, this topology is functional. However, an additional switch is needed. This leads to many problems regarding the system complexities, controls, high costs, and low efficiency [9].

Alternatively, the basic Z-source inverter (ZSI) [10], which exploits an impedance network composed of two inductors, two capacitors, and one diode, has been proposed to surmount the problems caused by the two-stage architecture. It utilizes the shoot-through (ST) mode of the inverter bridge (B6) to boost the input dc voltage via the impedance network in a single stage. Accordingly, ZSI technology has facilitated the evolution of various single-stage topologies. These topologies have garnered considerable discussions among researchers to improve efficiency, boost capability, and compactness.

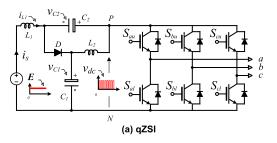

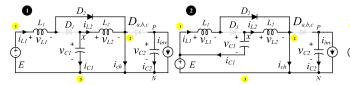

Several comprehensive reviews of the different ZSIs topologies and modulation techniques have been reported in the literature [11]–[17]. Among the plenteous structures of ZSIs, quasi-ZSI (qZSI) topology, shown in Fig. 1(a), is found to be more suitable for the PV, FC applications, multiport topologies, Electric-Vehicles (EVs), and electric drives applications due to its simple structure and continuous input current [17]–[19]. Notwithstanding this attractive utilization of the ZSI/qZSI in many applications, it suffers from common shortcomings that should be considered before utilizing these inverters in the industry. These shortcomings can be summarized as follows [11], [12]:

- 1) The ST intervals shrink the modulation region, give low voltage quality, and reduce the dc-bus utilization.

- 2) The dc-link voltage is pulsed with high dv/dt.

- 3) A long ST is needed to provide a high gain; hence, ZSIs would have to be operated under extreme conditions

FIGURE 1. Traditional single-stage boosting three-phase inverter topologies.

4) More passive components should be used to form an extended impedance source network to accomplish a high voltage gain with a short ST duration.

With the accelerated development of modern technologies, ZSIs demerits limit further industrial applications in some areas that require high boosting and inversion functions.

Recently, the SSI topology, shown in Fig. 1(b), has been suggested to surmount the ZSIs problems [20]. As can be seen from Fig. 1(b), this topology was acquired by combining the canonical dc-dc boost converter into the VSI, by connecting the boost inductor, L to the midpoint of each inverter leg (a, b, and c) via diodes  $(D_a, D_b, \text{ and } D_c)$ . Contrary to ZSIs, it can perform the boosting and inversion functions for a wide modulation index range. Theoretically, SSI obtains a proportional relationship to infinity between the voltage gain and modulation index with fewer passive elements. Also, it does not require the ST mode.

As a research hotspot, the basic topology of SSI has been extended to single-phase applications [21]-[24], multiport inverters [25], [26], and multilevel technologies [27], [28]. Moreover, it was explored for a wide range of applications [20]–[28]. However, the parasitic effects of the passive elements in SSI topology, which is based on the canonical step-up converter, significantly impact its boosting and output voltage gain. Consequently, the output voltage gain does not reach infinity in practice. As a result, the developments for the basic SSI are thus essential to achieve higher voltage gain. To the best of the authors' knowledge, scarce research works have focused on developing the SSI topology [29]-[31]. For example, a split-Y-source inverter has been introduced in [29], [30]. This topology increases the boosting factor and the voltage gain. Moreover, the voltage spikes, commonly generated in the Y-source impedance network, are avoided in this work. However, this topology is complex in implementation and has more passive elements.

Addressing this concern, this paper aims to develop the SSI topology to improve its boosting capability with a simple circuit structure. The developed topologies combine ZSI [10], quadratic boost dc-dc converter [32], and SSI features in a single circuit to obtain a square boosting in the dc-side. The newly obtained SSI topology is called Quadratic-Boost

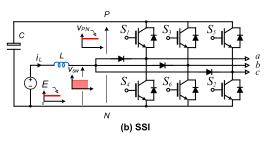

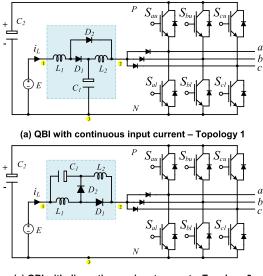

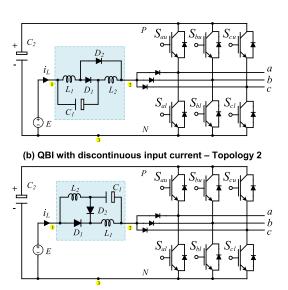

(c) QBI with discontinuous input current – Topology 3 FIGURE 2. Proposed QBI topologies.

SSI and is then termed by QBI. Four different topologies of the proposed QBI are introduced, as shown in Fig. 2. One with continuous input current (CC-QBI), and the other draws a discontinuous input current (DC-QBI) but with reduced capacitor voltage stresses. All topologies are modulated by the modified SVPWM scheme of the basic SSI. The main characteristics of these topologies compared to the previous boost inverters can be summarized as follows:

- 1) The basic spilt-source structure is retained.

- 2) Both boost and buck operations can be achieved.

- 3) Higher boosting and voltage gains are obtained.

- 4) It uses the conventional modulation schemes of SSI.

- 5) The CC-QBI has a continuous dc-current, while other architectures have a lower capacitor voltage.

However, it corresponds to the following demerits:

1) Like the basic SSI, unequal switch current sharing and power distribution are found compared to qZSI.

Given its many merits, this paper first introduces the proposed topologies and operating principles. The boosting factor and voltage gain are analyzed in detail for both ideal and considering the nonlinearities cases.

A modulation technique to reduce the inductor current ripples is presented. Moreover, the performance of the proposed topologies is assessed and compared with their counterparts. Finally, simulation and experimental results are given to confirm the theoretical findings.

# II. PROPOSED INVERTER TOPOLOGY AND ITS OPERATING MODES

#### A. TOPOLOGY

Four different topologies of the proposed QBI are shown in Fig. 2. In all topologies, the input inductance of the basic SSI,  $L_1$ , shown in Fig. 1(b) is replaced by an impedance cell. This cell is composed of two inductors,  $L_1$ ,  $L_2$ , capacitor,  $C_1$  and two diodes,  $D_1$ ,  $D_2$ . This combination is used to

(d) QBI with discontinuous input current – Topology 4

perform a cascaded boosting without additional switching states. The QBI, shown in Fig. 2(a), has a continuous input current compared to the others shown in Figs. 2(b)-(d). This is owed to the presence of the input inductance  $L_1$  in series with the supply, which buffers the supply current and reduces the supply stresses. Therefore, in the QBI with discontinuous input current (DC-QBI) of the Figs. 2(b)-(d), an additional input parallel capacitance with the supply is needed to mitigate input ripples' harmful effects. Nevertheless, the voltage stress on the capacitor  $C_1$  in the DC-QBI is lower than that of the QBI with continuous input current (CC-QBI). Moreover, all topologies feature a common dc-rail between the supply and inverter bridge. This connection reduces common-mode noise effects. The features of the proposed topologies are summarized in Table-1.

#### **B. OPERATING PRINCIPLES**

#### 1) MODES OF OPERATION

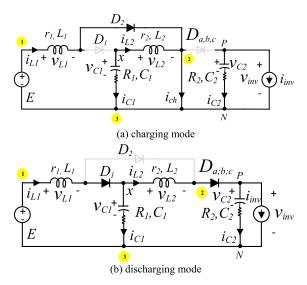

Inductive charging and discharging modes of operation can be observed in all QBI topologies. The ideal equivalent circuits during both modes are shown in Fig. 3. For the analysis's abridgment, the equivalent circuits of two different topologies are selected, the first one for the CC-QBI, shown in Fig. 2(a), and the other for the DC-QBI topology Fig. 2(b), as shown in Fig. 3.

# 2) STEADY-STATE ANALYSIS

In this section, the steady-state analysis of QBI topologies is reported. This analysis is simplified by considering an ideal case. In this analysis, the CC-QBI and DC-QBI topologies equations will be remarked by **0**, and **2**, respectively.

# a: INDUCTIVE CHARGING MODE

The charging mode can be obtained by switching ON at least one of the lower switches in the inverter bridge. In this case,

(a) charging mode of both CC-QBI 1 and DC-QBI 2, respectively.

FIGURE 3. Modes of operations of the proposed QBIs.

TABLE 1. Comparison between QBI topologies.

| Topologies | Supply<br>Current | $V_{C1}$ | Needs of<br>Input Cap. | dc-rail |

|------------|-------------------|----------|------------------------|---------|

| DC-QBI     | Discontinuous     | Low      | $\checkmark$           | Common  |

| CC-QBI     | Continuous        | High     | х                      | Common  |

the voltage at the output of the dc-side is zero due to the short-circuited. Besides, the diode  $D_1$  is blocking, while the diode  $D_2$  is conducting, as shown in Fig. 3(a). As a result, both inductors  $L_1$  and  $L_2$  are charged. By applying KVL, the following steady-state relationships during the charging duty cycle,  $D_{ch}$  can be observed.

#### b: INDUCTIVE DISCHARGING MODE

The discharging mode has only occurred when all the upper switches in the B6 are turned ON. In this case, the diode  $D_1$  will conducting, while  $D_2$  is in the blocking mode, as shown in Fig. 3(b), obtaining the following relation during a discharging duty cycle of  $D_{dis} = 1 - D_{ch}$ .

Based on the volt-second balance concept, the moving average voltage across the inductors over one switching period is zero (i.e.,  $\int_0^{T_s} v_L dt = 0$ ). From (1) to (2), we have

$$V_{L1} = \tilde{v}_{L1} = ED_{ch} + (E - v_{C1}) D_{dis} = 0 V_{L2} = \tilde{v}_{L1} = v_{C1}D_{ch} + (v_{C1} - v_{C2}) D_{dis} = 0, V_{L1} = \tilde{v}_{L1} = ED_{ch} - v_{C1}D_{dis} = 0 V_{L2} = \tilde{v}_{L1} = v_{xN}D_{ch} + (v_{xN} - v_{C2}) D_{dis} = 0$$

(3)

$v_{xN} = E + v_{C1}.$

(b) discharging mode of both CC-QBI (1) and DC-QBI (2), respectively.

FIGURE 4. Block diagram of MSVM schemes for QBI.

Thus, the voltage across the capacitors of both topologies is

$$\begin{aligned}

\mathbf{0} \begin{cases} V_{C1} = E / (1 - D_{ch}) = \beta_o E \\ V_{C2} = E / (1 - D_{ch})^2 = \beta_o^2 E \\ \mathbf{0} \end{cases} \\

\mathbf{0} \begin{cases} V_{C1} = E D_{ch} / (1 - D_{ch}) = (\beta_o - 1) E \\ V_{C2} = E / (1 - D_{ch})^2 = \beta_o^2 E \end{aligned}$$

(4)

where  $\beta_o$  is the dc-boosting factor of the basic SSI, and its value is defined by

$$\beta_o = 1/(1 - D_{ch})$$

(5)

It can be observed from (4) that the capacitor  $C_1$  voltage,  $V_{C1}$  in DC-QBI is much lower than that of CC-QBI as expected, while the voltage stress across the inverter switches, which is measured on the capacitor  $C_2$  are equals for both topologies.

#### 3) BOOSTING FACTOR AND AC VOLTAGE GAIN

Based on (4) the boosting factor, *B* of the QBI topologies, which is defined by the ratio of the average voltage across the inverter legs ( $V_{C2}$ ) to the input voltage, *E* can be written as

$$B = 1/(1 - D_{ch})^2 = \beta_o^2 \tag{6}$$

It is worth noting that the boosting factor of the proposed QBI gives a square relationship of the basic SSI topology.

Finally, the output ac voltage gain (G) is governed by

$$G = \frac{\hat{V}_{\phi 1}}{E} = \frac{BM_{ac}}{\sqrt{3}} = \frac{M_{ac}}{\left[\sqrt{3}\left(1 - D_{ch}\right)\right]^2}$$

(7)

where  $\hat{V}_{\phi 1}$  is the fundamental peak output phase voltage. It is worth noting that  $G \le 1/\sqrt{3}$  for conventional VSI.

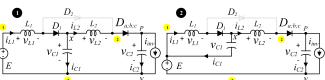

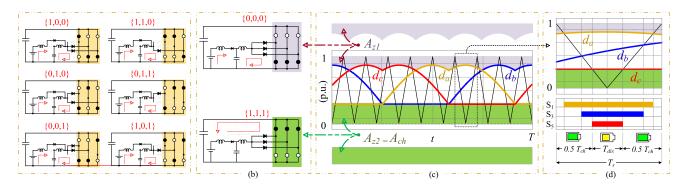

# C. MODULATION

Although all PWM schemes of the standard VSI can be used to modulate the proposed QBI switches to obtain the boosting

FIGURE 5. Modulation of quadratic-boost split-source inverter.

and inversion functions, modified unregulated and regulated SVPWM (MSVM and RMSVM) schemes, proposed in [20], and [33] represent the standard modulation approach of all extended-boost-based SSIs due to the following merits:

- It successfully ensures inductor charging and discharging with constant duty cycles. Consequently, lower input current ripples and voltage stresses are obtained.

- 2) It can be used to obtain the same performance as the two-stage topology.

In the carrier-based implementation of this scheme, the perphase duty cycles  $(d_a, d_b, d_c)$ , which are compared with the triangular high-frequency carrier-wave to generate the gating pulses of the B6 switches, can be defined by

$$\begin{bmatrix} d_a \\ d_b \\ d_c \end{bmatrix} = \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix} - \min(v_a, v_b, v_c) + (1 - \gamma)$$

(8)

where  $M_{ac}$  is the modulation index and,  $v_a$ ,  $v_b$  and  $v_c$  are the sinusoidal reference signals, which are governed by

$$\begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix} = \frac{M_{ac}}{\sqrt{3}} \begin{bmatrix} \cos\left(2\pi ft\right) \\ \cos\left(2\pi ft - 2\pi/3\right) \\ \cos\left(2\pi ft + 2\pi/3\right) \end{bmatrix}$$

(9)

The last term in (8) represents a constant upward shifting term of the duty cycles responsible for the boosting. In the MSVM scheme,  $\gamma$ , in (8) is equal to  $M_{ac}$  [20]. Therefore, both the dc-boosting factor, *B*, and the output voltage gains are controlled via the one control variable,  $M_{ac}$ . The RMSVM scheme give the inverter an additional control variable in the dc side by replacing  $\gamma$  in (8) by  $M_{dc}$  [33]. This yields to independent control between the dc and ac sides, which is necessary for the grid-connected applications and V/f control of the motor drives.

Figs. 4 and 5 show the implementation block diagram of the phase duty cycles generation and switching pattern of these modulation schemes, where the manual switch is used to select between the unregulated and regulated MSVM approach.

In the regulated modulation scheme, the QSI can be considered as two separate converters (i.e., quadratic boost dc-dc converter and VSI), and hence, the standard control modes can be implemented. Observing Fig. 5, the upper and lower

24166

switches for each leg of the B6 are commutated one per half switching cycle with variable duty cycles, like in the standard VSI.

Meanwhile, the overall inductive charging and discharging intervals ( $T_{ch}$  and  $T_{disch}$ ) are fixed since the minimum envelope of the per phase duty cycles is kept constant at  $(1 - \gamma)$  where  $\gamma$  equals to  $M_{dc}$ . However,  $M_{dc}$  must be higher than  $M_{ac}$  to ensure that the per phase duty cycles ( $d_a$ ,  $d_b$ ,  $d_c$ ) remain less than 1 (i.e.: the carrier amplitude) and hence maintaining in linear modulation region. Based on the voltsecond balance concept, the inductor L is charged with

$$D_{ch} = M_{dc} \tag{10}$$

From (6), (7), and (10), the boosting factor, *B*, and ac-voltage gain of the proposed QBI using the RMSVM scheme are

$$\begin{cases} B = 1/(1 - M_{dc})^2 \\ G = M_{ac}/\left\{\sqrt{3}(1 - M_{dc})^2\right\} \end{cases}$$

(11)

It can be noticed from (10) that, when  $M_{dc}$  ranges from 0 to 1, the booting factor, *B* vary from 1 to infinity. However, due to the parasitic effects of the modulation deadtime and passive elements of the QSI, the boosting factor in practice is limited. On the other hand, the proposed topology can be used for the buck operating mode. This mode can be achieved by canceling the upward shifting term in (8) or by setting  $M_{dc}$  by one. In the following section, an analytical study of the proposed QBI topology considering the inverter nonlinearities is presented.

#### III. MODELING OF THE PROPOSED TOPOLOGY CONSIDERING THE NONIDEALITIES

For simplicity, the CC-QBI topology is only considered in the analysis due to its merits and the suitability of the applications. Fig. 6 shows the nonideal equivalent circuits of the CC-QBI by considering the effect of the inductor parasitic resistance and equivalent series resistance of the capacitors. In this section, the state-space averaging approach of the CC-QBI, assuming continuous condition mode, is described and used to derive the quiescent dc and small-signal ac equations of the analyzed topology.

FIGURE 6. Equivalent circuit Of CC-QBI with nonlinearities.

#### A. STATE-SPACE AVERAGING MODEL

As in the ideal case analysis, the operation of QBI is divided into inductive charging and discharging modes. In both modes, the independent states of the inverter are the inductor currents,  $i_{L1}$ ,  $i_{L2}$  and the capacitor voltages,  $v_{C1}$ ,  $v_{C2}$ . Therefore, the state vector x(t) can be defined as

$$x(t) = \begin{bmatrix} i_{L1} & i_{L2} & v_{C1} & v_{C2} \end{bmatrix}^T$$

(12)

The input and output variables, u(t) and y(t) are defined by

$$u(t) = \begin{bmatrix} e \ i_{inv} \end{bmatrix} \tag{13}$$

$$y(t) = v_{inv} \tag{14}$$

where *e* is the input-dc voltage,  $i_{inv}$  is the dc-link current, and  $v_{inv}$  is the output voltage of the dc-side, which can also be defined as the inverter bridge voltage.

During the charging mode of the duty cycle  $d = d_{ch}$ , the dc-side of the inverter is reduced to the linear circuit of Fig. 6(a), which the following state-space equations can describe:

$$\begin{cases} \dot{x}(t) = A_1 x(t) + B_1 u(t) \\ y(t) = C_1 x(t) + D_1 u(t) \end{cases}$$

(15)

where

$$A_{1} = \begin{bmatrix} -\frac{r_{1}}{L_{1}} & 0 & 0 & 0\\ 0 & -\frac{R_{1}+r_{2}}{L_{2}} & \frac{1}{L_{2}} & 0\\ 0 & -\frac{1}{C_{1}} & 0 & 0\\ 0 & 0 & 0 & 0 \end{bmatrix}, \quad B_{1} = []$$

$$C_{1} = \begin{bmatrix} 0 & 0 & 0 & 1 \end{bmatrix}, \quad D_{1} = \begin{bmatrix} 0 & -R_{2} \end{bmatrix} \quad (16)$$

With the zero-state,  $V_7$ , the inverter is in the discharging mode for the duty cycle of  $d' = 1 - d_{ch}$ . The equivalent linear circuit of this mode is shown in Fig. 6(b). It can be described by the following state-space equation

$$\begin{cases} \dot{x}(t) = A_2 x(t) + B_2 u(t) \\ y(t) = C_2 x(t) + D_2 u(t) \end{cases}$$

(17)

where

$$A_{2} = \begin{bmatrix} -\frac{R_{1}+r_{1}}{L_{1}} & \frac{R_{1}}{L_{1}} & -\frac{1}{L_{1}} & 0\\ \frac{R_{1}}{L_{2}} & -\frac{R_{1}+R_{2}+r_{2}}{L_{2}} & \frac{1}{L_{2}} & -\frac{1}{L_{2}}\\ \frac{1}{C_{1}} & -\frac{1}{C_{1}} & 0 & 0\\ 0 & \frac{1}{C_{2}} & 0 & 0 \end{bmatrix}$$

$$B_{2} = \begin{bmatrix} 1/L_{1} & 0 & 0 & 0\\ 0 & 0 & 0 & 0 \end{bmatrix}^{T}$$

$$C_{2} = \begin{bmatrix} 0 & R_{2} & 0 & 1 \end{bmatrix}, \quad D_{2} = \begin{bmatrix} 0 & 0 \end{bmatrix}$$

(18)

So, the matrices  $A_1$ ,  $B_1$ ,  $C_1$ , and  $D_1$  for the charging mode and  $A_2$ ,  $B_2$ ,  $C_2$ , and  $D_2$  for the discharging mode are defined. Given these matrices, the averaged state-space model (largesignal model) can be defined by

$$\begin{aligned} \dot{x}(t) &= \bar{A}x(t) + \bar{B}u(t) \\ y(t) &= \bar{C}x(t) + \bar{D}u(t) \end{aligned}$$

(19)

where the matrices  $\bar{A}$ ,  $\bar{B}$ ,  $\bar{C}$  and  $\bar{D}$  are evaluated by applying the state-space averaged equilibrium equations of (20),

$$\begin{aligned}

\left[ \begin{array}{l} \bar{A} = A_1 d + A_2 d' \\

\bar{B} = B_1 d + B_2 d' \\

\bar{C} = C_1 d + C_2 d' \\

\bar{D} = D_1 d + D_2 d'

\end{aligned} (20)$$

#### **B. STEADY-STATE DC-MODEL**

If the inverter is driven with the steady-state at the quiescent operating point, the duty cycle, d and input voltage, e in the state-space model of (19) and (20) are equal  $D_{ch}$  and E, respectively. The steady-state model can be derived from a large-signal model by setting ( $\dot{x}(t) = 0$ ) and hence:

$$\begin{cases} 0 = \bar{A}X + \bar{B}U \\ Y = \bar{A}X + \bar{B}U \end{cases}$$

(21)

where X, U, and Y are the state, input, and output variables at steady-state, respectively.

Solving (21) to find the equilibrium state and output vectors

$$\begin{cases} X = -\bar{A}^{-1}\bar{B}U \\ Y = \left(-C\bar{A}^{-1}\bar{B} + \bar{D}\right)U \end{cases}$$

(22)

This results in the following steady-state equations

$$\begin{cases} I_{L1} = \frac{1}{1 - D_{ch}} I_{L2} \\ I_{L2} = \frac{D_{ch}}{1 - D_{ch}} I_{INV} \end{cases}$$

TABLE 2. System parameters and operating conditions used for the frequency analysis.

FIGURE 7. Nonideal dc-voltage boosting and ac-voltage gain of the proposed CC-QBI.

$$\begin{cases} V_{C1} = \frac{E}{1 - D_{ch}} - V_u \\ V_{C2} = V_{inv} = \frac{E}{(1 - D_{ch})^2} - V_w \end{cases}$$

(23)

where

$$\begin{cases} V_u = \left( D_{ch} R_1 + \frac{r_1}{1 - D_{ch}} \right) I_{L1} \\ V_w = \left( \frac{D_{ch} R_1}{1 - D_{ch}} + \frac{r_1}{(1 - D_{ch})^2} \right. \\ \left. + D_{ch} r_2 + (1 - D_{ch}) R_2 \right) I_{L1} \end{cases}$$

(24)

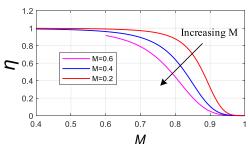

It is worth noting that the same steady-state equation in the ideal case can be obtained from (23) and (24) by neglecting the nonlinear effects of the parasitic resistance of the inductors and the ESR of the capacitors. Figs. 7 and 8 show the plot of dc-boosting, ac-voltage gain, and inverter efficiency considering the nonideal circuit parameters of Table 2 at different modulation indices. It is evident how the increase of the inductor's parasitic resistance and ESR of the capacitors reduce the boosting and ac-voltage gains to zero at high duty cycles, although ideally, it is supposed to obtain a quite large value. Moreover, it can be observed that the parasitic resistances significantly reduce the boosting factor than that of the ESRs. For these reasons, a very low impact of the parasitic resistances should be considered in the design to improve the boosting capability and inverter efficiency.

#### C. SMALL-SIGNAL AC-MODEL

The small-signal model can be obtained by linearizing all the variables in the state-space averaging model around the equilibrium (steady-state) point. This can be done by

FIGURE 8. Nonideal dc-voltage boosting, and ac-voltage gain of the proposed CC-QBI.

assuming that any variable equals steady-state value plus a superimposed small, perturbed ac variable and neglecting the high-order nonlinear terms. Hence, the state equations of the small-signal ac model are

$$\begin{cases} \dot{\tilde{x}} = \bar{A}\tilde{x} + \bar{B}\tilde{u} + [(A_1 - A_2)X + (B_1 - B_2)U]\tilde{d} \\ \tilde{y} = \bar{C}\tilde{x} + \bar{D}\tilde{u} + [(C_1 - C_2)X + (D_1 - D_2)U]\tilde{d} \end{cases}$$

(25)

where  $\tilde{x}$ ,  $\tilde{u}$ ,  $\tilde{d}$ , and  $\tilde{y}$  are the small-perturbed ac variations about the steady-state solution or the quiescent operating point defined by (20)-(24).

Therefore, the linearized ac small-signal state-space model of the proposed topology can be written as

$$\begin{cases} \dot{\tilde{x}} = \mathcal{A}\tilde{x} + \mathcal{B}\tilde{u} \\ \tilde{y} = \mathcal{C}\tilde{x} + \mathcal{D}\tilde{u} \end{cases}$$

(26)

where  $u = \begin{bmatrix} e & i_{inv} & d \end{bmatrix}^T$

# D. CC-QBI TRANSFER FUNCTION

This section uses the small-signal model of the CC-QBI derived in the previous section to obtain the system transfer functions. Using Laplace Transformation of (26) yields

$$\begin{cases} x(s) = [sI - \mathcal{A}]^{-1} \mathcal{B}u(s) \\ y(s) = \left( \mathcal{C} [sI - \mathcal{A}]^{-1} \mathcal{B} + D \right) u(s) \end{cases}$$

(27)

Consequently, it is possible to express the dc-link voltage of the CC-QBI,  $v_{inv}(s) = y(s)$  as follows

$$v_{inv}(s) = G_{dv}(s) d(s) + G_{ev}(s) e(s) + G_{iv}(s) i_{inv}(s)$$

(28)

Moreover, the input current,  $i_1$  can be expressed as

$$i_1(s) = \left( \acute{\mathbb{C}} \left[ sI - A \right]^{-1} \mathscr{B} + \acute{\mathbb{D}} \right) u(s)$$

(29)

where  $\hat{C} = \begin{bmatrix} 1 & 0 & 0 & 0 \end{bmatrix}$  and  $\hat{D} = \begin{bmatrix} 0 & 0 & 0 \end{bmatrix}$ . This yields to

$$i_1(s) = G_{di}(s) d(s) + G_{ei}(s) e(s) + G_{ii}(s) i_{inv}(s)$$

(30)

where  $G_{dv}$ ,  $G_{ev}$ , and  $G_{iv}$  are the duty, input voltage, and input current to dc-link voltage transfer functions. Also,  $G_{di}$ ,  $G_{ei}$ , and  $G_{ii}$  are the transfer functions of duty, input voltage, and output dc-link current to the input current.

FIGURE 9. Signal flow graph of the CC-QBI.

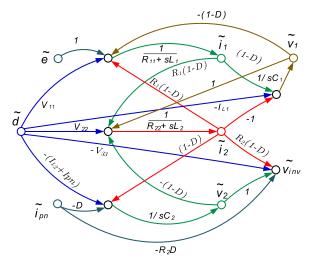

From (28) and (30), the signal flow graph (SFG) of the proposed QBI can be obtained, as shown in Fig. 9, where

$$V_{11} = R_1 I_1 - R_1 I_2 + V_1$$

$$V_{22} = R_2 I_2 - R_1 I_1 + V_2$$

$$V_{33} = R_2 I_2 + R_2 I_{pn}$$

$$R_{11} = r_1 + (1 - D) R_1$$

$$R_{11} = r_2 + (1 - D) R_2 + R_1$$

(31)

As observed from the SFG of Fig. 9, the sources of disturbances and variations in the proposed inverter are many. The following section desires to obtain the frequency domain analysis despite the disturbance of the duty cycle.

#### E. FREQUENCY DOMAIN ANALYSIS

The transfer functions of (24) and (26) describe how the disturbances in the input variables lead to disturbances in

the output variables of the dc-side of the proposed topology. For the sake of illustration, if the proposed topology is used for grid-connected PV systems, the dc-link voltage,  $v_{inv}$  will be controlled via the inverter bridge and, the input voltage variation held to zero due to the MPPT regulator, then the perturbation of  $v_{inv}$  and e are neglected. This yields to

$$\begin{cases} i_{pn}(s) = -\frac{G_{dv}(s)}{G_{iv}(s)}d(s) \\ G(s) = \frac{i_1(s)}{d(s)}\Big|_{\substack{v_{inv}=0\\e=0}} = G_{di}(s) - \frac{G_{ii}(s) G_{dv}(s)}{G_{iv}(s)} \end{cases}$$

(32)

The transfer function G of (28) describes how the variation of the duty cycle input influence the input current of the inverter. It is worth noting that in the grid-connected PV systems, G is the key component of the control system and has a significant effect on the grid-tie inverter performance.

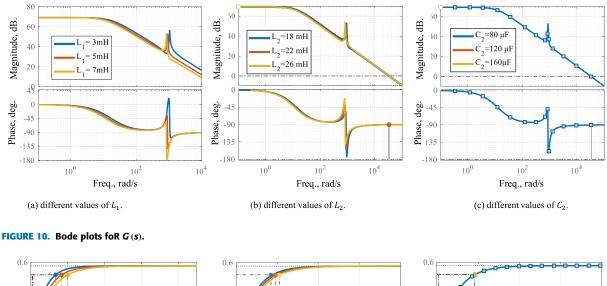

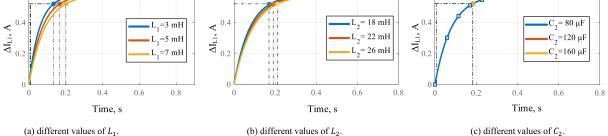

The Bode plot of Fig. 10 and the time responses of Fig. 11 for the transfer function in (32) are used to optimize the design parameters. Fig. 10(a) shows the Bode diagram under changing of  $L_1$  and  $L_2$  for specific parameters and steadystate operating conditions indicated in Table 2. It can be observed that as  $L_1$  decreases, the cutoff frequency and hence the bandwidth increases, which results in a faster response, as indicated in Fig. 11(a), which shows the time response for a step-change in the duty cycle. However, a lower  $L_1$ results in higher input current ripples. Therefore, a comprise between dynamic response and current ripples should be achieved. On the other hand, variation of  $L_2$  has a slight effect on the dynamic response (as  $L_2$  decrease the response goes slightly faster) as shown in Fig. 10(b) and Fig. 11(b), while the variation  $C_2$  do not affect the response speed. However, a higher value of  $C_2$  results in a lower ripple in the dc-link voltage. Also, variation of  $C_1$  do not affect the speed of response.

$$\mathcal{A} = \begin{bmatrix} -\frac{1}{L_1} [r_1 + (1-D)R_1] & R_1 \frac{1-D}{L_1} & -\frac{1-D}{L_1} & 0 \\ R_1 \frac{1-D}{L_2} & -\frac{1}{L_2} [R_1 + r_2 + (1-D)r_2] & \frac{1}{L_2} & -\frac{1-D}{L_2} \\ \frac{(1-D)}{C_1} & -\frac{1}{C_1} & 0 & 0 \\ 0 & \frac{1-D}{C_2} & 0 & 0 \end{bmatrix}$$

$$\mathcal{B} = \begin{bmatrix} \frac{1}{L_1} & 0 & \frac{1}{L_1} [R_1 J_{L1} - R_1 J_{L2} + V_{C1}] \\ 0 & 0 & \frac{1}{L_2} [-R_1 I_{L1} + R_2 J_{L2} + V_{C2}] \\ 0 & 0 & -\frac{I_{L1}}{C_1} \\ 0 & -\frac{D}{C_2} & -\frac{I_2}{C_2} - \frac{I_{INV}}{C_2} \end{bmatrix}$$

$$\mathcal{C} = \begin{bmatrix} 0 & R_{C2} (1-d) & 0 & 1 \end{bmatrix}$$

**FIGURE 11.** Time response of the source current due to a small step increase of the duty cycle ( $\Delta d = 0.0002$ ).

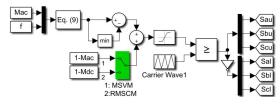

#### **IV. COMPARATIVE ASSESSMENT**

This section introduces a detailed comparative assessment between the presented single-stage inverter topologies, including qZSI, SSI, and proposed QBI. This assessment covers the following aspects: modulations complexity, steadystate analysis, current and voltage stresses, and the passive components requirements. The losses and inverter efficiency are explored in the simulation study using PLECS.

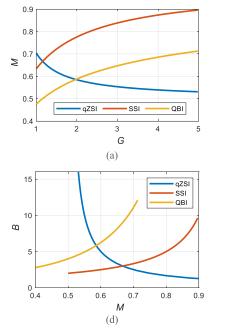

Table 3 summarizes the comparison results between the analyzed topologies regarding the duty cycles, boosting factors, voltage stresses on capacitors and semiconductors, and the ac-voltage gain of different topologies. Moreover, Figs. 12-14 give better representations of the boosting and performance characteristics of these topologies.

Note that all topologies are controlled by the MSVM technique, presented in [34] for qZSI and in [20] for SSI topology to obtain a fair comparative study.

#### A. IMPLEMENTATIONS

The implementation procedure of power converters' modulation techniques represents an important issue that should be considered in comparing the different topologies.

The modulation technique complexity can be determined based on different factors such as the number of duty cycles and the possibility of utilizing the enhanced PWM (ePWM) modules of modern DSPs in the implementation. Table 2 compares the analyzed topologies regarding the required number of duty cycles and the complexity of utilizing the ePWM modules used in the implementation aspects. The modulation of basic SSI and proposed QBI is more straightforward than that of qZSI, which requires more duty cycles in addition to the high specifications of DSP controllers due to its complexity.

#### **B. VOLTAGE GAINS AND BOOSTING ABILITY**

Table 3 lists more evident steady-state comparisons among the analyzed topologies in terms. To be fair, these relations are plotted for the same gain range. Considering limitations due to parasitic elements, the voltage gain range is chosen as  $G \le 5$ . The relations between the boosting factor, charging duty cycles, and the voltage gains for the analyzed topologies are shown in Fig. 12, and the following conclusions can be made:

- 1) The boosting action of qZSI is valid for  $D_{ch} < 1/2$ , while in SSI and QBI,  $D_{ch}$  has a broader range with  $D_{ch} < 1$ .

- 2) The SSI and proposed QBI topologies have more voltage gain capability compared to qZSI.

- 3) The boosting ability of the QBI is significantly higher than that of the basic SSI for the exact charging duty cycle. This is owed to the squaring feature of the dc-boost factor.

- 4) SSI has the lowest boosting factor compared with the other topologies for the same voltage gains. Thus, SSI

TABLE 3. Comparisons of the proposed QBI with For qZSI and SSI.

| Topology                                    |                      | qZSI <sup>(*)</sup> [34]         | SSI <sup>(‡)</sup> [20]                            | CC-QBI (*)               | DC-QBI (*)                  |

|---------------------------------------------|----------------------|----------------------------------|----------------------------------------------------|--------------------------|-----------------------------|

| Number of<br>duty cycles                    |                      | 5                                | 3                                                  | 3                        | 3                           |

| Utilizing<br>ePWM                           |                      | Complex                          | Simple                                             | Simple                   | Simple                      |

| Charging<br>duty cycle, $1 - M$<br>$D_{ch}$ |                      | М                                | М                                                  | М                        |                             |

| Number<br>inductor                          |                      | 2                                | 1                                                  | 2 2                      |                             |

| Number of<br>capacitors                     |                      | 2                                | 1                                                  | 2                        | 2                           |

| Boosting fa<br>B                            | Boosting factor, $B$ |                                  | $\frac{1}{1-D_{ch}} \qquad \frac{1}{(1-D_{ch})^2}$ |                          |                             |

| dc-voltage                                  | $, V_{dc}$           | Pulsed                           |                                                    | Continuous               |                             |

| vonage gam,                                 |                      | $\frac{M}{\sqrt{3}(1-M)}$        |                                                    |                          |                             |

| Capacitor $\frac{V_c}{E}$                   | $\frac{V_{C_1}}{E}$  | $\frac{1 - D_{ch}}{1 - 2D_{ch}}$ | -                                                  | $\frac{1}{1 - D_{ch}}$   | $\frac{D_{ch}}{1 - D_{ch}}$ |

| voltage                                     | $\frac{V_{C_2}}{E}$  | $\frac{D_{ch}}{1-2D_{ch}}$       | $\frac{1}{1 - D_{ch}}$                             | $\frac{1}{(1-D_{ch})^2}$ | $\frac{1}{(1-D_{ch})^2}$    |

| Efficiency (‡)                              |                      | 89%                              | 93%                                                | 91%                      | 91%                         |

|                                             |                      |                                  |                                                    |                          |                             |

(\*) qZSI, in this study, is controlled using the MSVM scheme given in [34].

(‡) SSI and QBI are controlled using the MSVM scheme given in [20].

(‡) Efficiency is determined by PLECS for 1kVA, and voltage gains.

will produce lower voltage stresses on the B6 semiconductors. However, qZSI produces a higher boosting factor for G > 2. Therefore, it has higher voltage ratings than B6 devices.

Low modulation indexes are required to obtain high voltage gains in the qZSI. Hence, the distorted output voltage is expected in the qZSI than the other topologies.

# C. CAPACITOR VOLTAGES AND INDUCTOR CURRENT RIPPLES

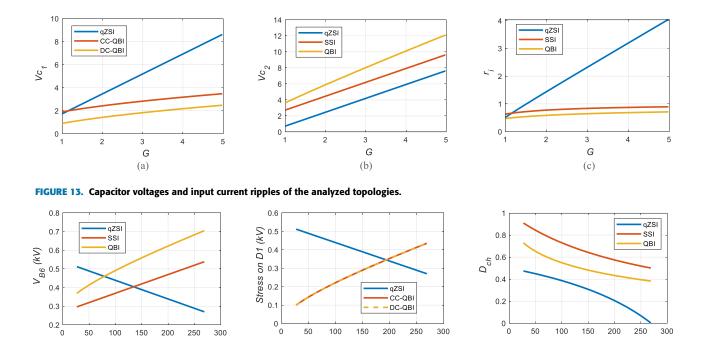

The voltage stress and input current ripples are essential factors that should be carefully considered in any converter design. It determines the cost, weight, and volume of the converter. Table 3 lists the capacitor voltages of the analyzed topologies. Besides, Figs. 13(a) and 13(b) sketch the variations of these voltages versus gain, G.

# 1) CAPACITOR VOLTAGES

Regarding the voltage stress on the capacitor  $C_1$ . It can be seen from Fig. 13(a) that, qZSI has the highest voltage stress. Meanwhile, the CC-QBI topology has slightly higher voltage stress on the capacitor  $C_1$ . However, the DC-QBI introduces much lower voltage stress on  $C_1$ . From Fig. 13(b), qZSI has the minimum voltage stress on the capacitor  $C_2$ .

#### 2) INPUT CURRENT RIPPLES

As far as the input current ripples of the analyzed topologies are concerned, the instantaneous current ripples  $\Delta I_i$  in each topology is investigated. The focus will be on the same input and output conditions. By applying Kirchhoff's voltage law for the equivalent circuits of the analyzed topologies in the inductive charging modes and after some derivation's steps, the normalized input current ripples,  $r_i$  can be given by

$$r_{i} = \frac{\Delta I_{i}}{k}$$

$$= \begin{cases} D_{S}, \qquad \Rightarrow \text{SSI} \\ D_{q} (1 - D_{q}) / (1 - 2D_{q}), \quad \Rightarrow \text{qZSI} \\ D_{QB}, \qquad \Rightarrow \text{CC-QBI} \end{cases}$$

(33)

0.6 D 0.4 aZSI SSI QBI 0.2 2 3 4 5 G (b) 15 aZSI SSI QBI 10 Ξ 5 0.2 0.4 0.6 0.8 D<sub>ch</sub>

(e)

0.8

FIGURE 12. Voltage gain and the boosting ability of the analyzed topology.

E (V)

(b)

FIGURE 14. Semiconductor stresses analysis of the analyzed topologies versus E for a constant output voltage of 110V/phase.

where k is a constant ( $k = ET_s/L_1$ ) and  $D_q$ ,  $D_S$  and  $D_{QB}$  are charging duty cycles of the qZSI, SSI, and QBI, respectively.

E(V)

(a)

Fig. 13(c) shows input current ripples dependency,  $r_i$  of the analyzed topologies versus the output gain. It can be observed that the proposed QBI has lower input current ripple than the other topologies, while the ripple of qZSI is high.

#### **D. REQUIRED INDUCTANCES**

Applying the volt-second balanced concept on the QBI dc-side with the MSVM scheme, it can be found that the input inductance,  $L_1$  for CC-QBI can be determined from

$$L_1 = EM_{QB}/\left(f_s \cdot \Delta I_1\right) \tag{34}$$

where  $I_1$  is the current in the inductor  $L_1$ ,  $f_s$  is the effective switching frequency, which equals the carrier frequency in the MSVM scheme, and  $\Delta I_1$  is the input current variation. The relation between currents flowing in the two inductors ( $I_1$  and  $I_2$ ) at the dc-side of QBI is governed by

$$I_1 = I_2 / \left( 1 - M_{QB} \right) \tag{35}$$

Thus, to obtain the same current ripple of the two inductors, the required inductance  $L_2$  should be evaluated from

$$L_2 = L_1 / \left( 1 - M_{QB} \right) \tag{36}$$

On the other hand, the inductances of the SSI and qZSI topologies can be determined from [20], [34]

$$\begin{cases}

L = \frac{E}{f_s \cdot \Delta I_1} M_s, & \text{for SSI} \\

L = \frac{E}{f_s \cdot \Delta I_1} \frac{M_q (1 - M_q)}{2M_q - 1}, & \text{for qZSI}

\end{cases}$$

(37)

For a fair comparison between the analyzed topologies, the modulation indexes ( $M_q$ ,  $M_S$ , and  $M_{QB}$ ) should be determined for the same output voltage gain. Based on (33)-(36), to obtain the same current ripples in the analyzed topologies, the qZSI requires larger inductance than SSI and the proposed QBI, which requires the lower one.

E(V)

(c)

#### E. INVERTER VOLTAGE STRESSES

#### 1) VOLTAGE STRESS

Considering the circuits of the analyzed topologies, it can be found that the voltage stress on all switches of the inverter bridges is equal to the peak dc-link voltage or the voltage across the capacitor  $C_2$ ,  $\hat{v}_{C2}$ . Therefore, for the same gain, the switch voltage stress,  $v_{B6}$  normalized to the input voltage of the analyzed topologies can be determined from

$$\frac{v_{B6}}{E} = \begin{cases} \left(2\sqrt{3} G - 1\right), & \Rightarrow qZSI \\ \left(\sqrt{3} G + 1\right), & \Rightarrow SSI \\ \frac{6G^2}{1 + 2\sqrt{3} G + \sqrt{1 + 4\sqrt{3} G}}, & \Rightarrow QBI \end{cases}$$

(38)

Fig. 12(f) shows the dependency of the boosting factor, B, versus output gain, G, whereas Fig. 14 shows the variation of common semiconductor voltage stresses, with E for a constant output voltage of 110Vrms/phase.

From these results, it can be observed that

- 1) The SSI has the minimum voltage stress on B6 and the front-end diode when a high voltage gain is required.

- The qZSI has the minimum voltage stress on B6 and the front-end diode for the high input voltage region, which requires low gains to obtain the same output voltage.

FIGURE 15. Closed-loop control of the proposed QBI.

TABLE 4. Measurements of the analyzed topologies for the case study.

| Topology                |                                   |        | qZSI   | SSI    | QBI    |

|-------------------------|-----------------------------------|--------|--------|--------|--------|

| DC-Link Voltage         |                                   |        | 492V   | 319.5V | 413.2V |

| Input Current           |                                   | 20A    | 20A    | 20A    |        |

| Input Current ripples   |                                   | 5.6A   | 2A     | 1.48A  |        |

| Output Voltage THD      |                                   | 114.4% | 71.3%  | 97.99% |        |

| Average dc-Link voltage |                                   | 269.6V | 319.5V | 413.2V |        |

| C                       | Capacitor Voltage, C <sub>1</sub> |        | 219.8V | -      | 143.7V |

|                         | Max.                              | Upper  | 44A    | 7A     | 8A     |

| ent                     | E Max.                            | Lower  | 40A    | 25A    | 33A    |

| SSS                     | A                                 | Upper  | 6.7A   | 1.3A   | 0.9A   |

| B6 Current<br>stress    | Average                           | Lower  | 0.7A   | 6.8A   | 6.3A   |

| B6                      | RMS                               | Upper  | 15A    | 2.2A   | 1.8A   |

|                         |                                   | Lower  |        | 12.5   | 14A    |

3) Meanwhile, the SSI employs slightly higher voltage stress, especially for high input voltage regions.

# 2) CURRENT STRESS

In practice, the presented topologies' current stresses are different under different modulation schemes and load conditions. For comparisons, evaluating the current stress on the inverter bridge's switching devices will be presented in the simulation study.

# F. DISCUSSION

Based on the preceding theoretical analyses, a study of four different topologies of quadratic boost split-source inverters is introduced, displaying the main characteristics. Based on the comparative study given in this paper, it can be concluded that among these topologies, the CC-QBI has superior characteristics. It has a good performance compared with the other QBI topologies, SSI and qZSI when operating with a low input voltage. This means that the proposed topology is suitable for PV, FC, and Electric Vehicle (EV) applications.

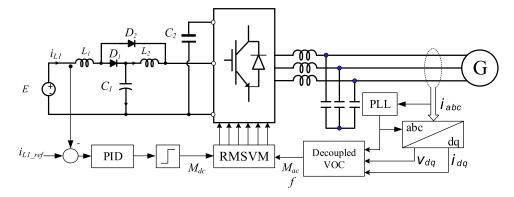

#### V. CLOSED-LOOP CONTROL OF QBI TOPOLOGY

The block diagram of the closed-loop control of the QBI for the grid-connected system is shown in Fig. 15. In this technique, the regulated MSVM presented in section II is used. The dc-link voltage is controlled via decoupled

voltage-oriented control (VOC) through output current controllers and the dc-link voltage controller with the modulation index of the standard VSI as the manipulating variable. The input current,  $i_{L1}$  is adopted by controlling  $M_{dc}$  value as shown in Fig. 15. It should be noticed that the input current can be controlled to control the power required to supply the load in case of a constant voltage source or can be used to track the maximum available power in case of a PV source.

#### **VI. SIMULATION RESULTS**

#### A. CASE-I: STEADY-STATE ANALYSIS

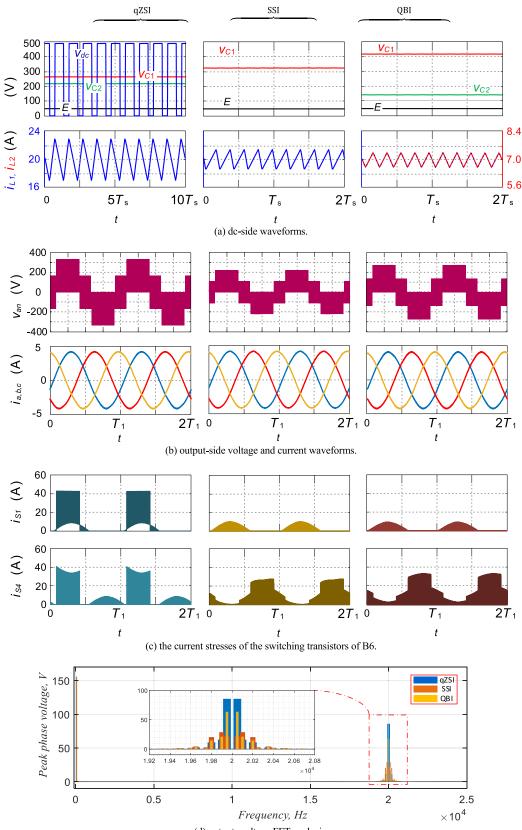

Three-phase qZSI, SSI, and CC-QBI topologies using MSVM techniques are modeled via MATLAB and PLECS platforms to investigate their functionality and verify the comparative study analysis. A dc-supply of 50V is used in all topologies, while three-phase loads of 1kVA, 50Hz, 0.95 lagging power factor at 110V/phase are connected at the output. Figs. 16-18 and Table 4 show the simulation results.

The modulation indices in the qZSI, SSI, and CC-QBI topologies are set at 0.5511, 0.8435, and 0.6521, respectively, to generate the same output phase voltages of 110V from the 50V dc-supply. The same inductance and capacitances of 1.25mH and 120 $\mu$ F, respectively, are used in all topologies to show these effects on the input current and dc-voltage ripples. Table 4 shows the measured voltage and current from the presented topologies' simulation models, where Fig. 16 shows the obtained results, which compares the proposed QBI with that of basic SSI and qZSI. Fig. 16(a) illustrates the voltage and current waveforms of the dc-side of the analyzed inverters, while Fig. 16(b) shows the output voltage, current waveforms, and the FFT analysis of the voltage. The current stress on the upper and lower switch in one leg of the analyzed topologies is shown in Fig. 16(c) at the same operating conditions. From these results, it can be observed that,

- 1) The measured values of Table 4 show a good agreement with that estimated from the analysis.

- In all topologies, the output phase currents, as well as the average values of input current are very close. Moreover, the load currents exhibit near sinusoidal waveforms.

(d) output- voltage FFT analysis.

FIGURE 16. Simulation results of the one kVA qZSI, SSI, and QBI using the modified SVPWM techniques.

FIGURE 17. Simulation results of a step change of the output voltage.

- 3) The proposed QBI has a lower input current ripple than the other topologies, as shown in Fig. 16(a). Its current ripple is reduced by about 74% and 26% compared with qZSI and SSI values, respectively.

- The dc-link voltage of the qZSI is pulsed with the highest value of 492V compared with the other topology. This leads to higher voltage stresses on the inverter bridge.

- 5) The same output voltage magnitude with a peak of  $110\sqrt{22V}$  is obtained, as shown in the FFT analysis of Fig. 16(b). Moreover, the output voltage of the proposed QBI has a lower THD than qZSI, while the SSI has the least THD value. This is owed to using different modulation indexes to give the same output voltage in all topologies.

- 6) From the viewpoint of active switch current stress in the analyzed topology, the switch currents are determined by the output current, average input current, the peak-to-peak inductor current ripple, and the inductive charging and discharging methods. Since the same input and output conditions are considered in this study, the switch currents are significantly affected by the method of charging and discharging, as shown in Fig. 16(c). Due to the utilization of both switches in the inverter leg for ST state in the qZSI, the switch current is increased simultaneously. Hence, it is worth comparing the current stress of qZSI topology with that of the SSI and proposed QBI.

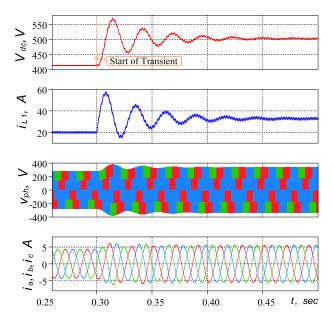

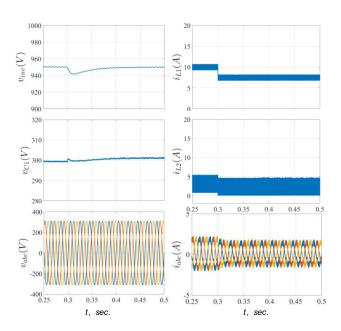

With the selected case study, Fig. 17 shows the simulation results of dc-link voltage, input current and output phase voltage, and currents of the QBI around the instant of step transition of the modulation index, which affect the output voltage. In t = 0.3 sec., the modulation index is increased by 5% from its initial value (i.e., it changed from 0.652 to

| TABLE 5. P | Parameters for | r power loss | calculation. |

|------------|----------------|--------------|--------------|

|------------|----------------|--------------|--------------|

| Parameters            | Values      | Parameters     | Values  |

|-----------------------|-------------|----------------|---------|

| MOSFETs               | IPW60R280P6 | ESR at 650V    | 50e-3   |

| Diodes                | IDW75E60    | Output Voltage | 220Vrms |

| Parasitic Resistances | 0.12        | Input Voltage  | 100V    |

0.684). The captured waveform clearly illustrates the smooth dynamic transition between the two cases as can be theoretically predicted. Some overshoot with low-frequency transient is observed and it will be damped via the closed-loop operation.

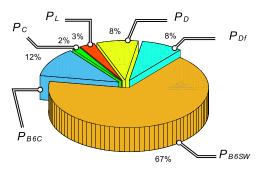

Moreover, the inverter losses including switching and condition losses of the analyzed topologies are studied using PLECS and the results are shown in Fig. 18. Since the semiconductor loss analysis depends on the characteristics of the employed devices, Table 5 lists the parameters of the utilized modules in the PLECS thermal analysis. The used modules are the Infineon-MOSFET of IPW60R280P6 and the fastswitching diode of IDW75E60. Only the copper loss in the inductors is considered and determined based on the RMS current through the inductor as

$$P_{cu} = r_L \cdot I_{L,rms}^2$$

$$P_{cu} = R_C \cdot I_{C,rms}^2$$

(39)

where  $r_L$  and  $R_C$  are the inductor's and ESR resistances, and  $I_L$  and  $I_C$  are the RMS inductor and capacitor currents, which are determined using PLECS.

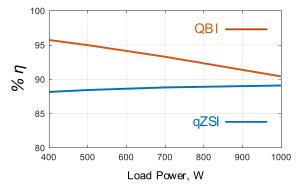

Fig. 18 shows the losses distribution of 1kVA QBI. It can be observed that the switching and conduction losses in the B6 switches are significant. This is owed to the utilization of the inverter switches in the inductive charging and discharging processes. Also, Fig. 19 compares the efficiency of the proposed QBI and the qZSI considering the same operating conditions and losses in passive elements. It can be found that the proposed QBI has a larger efficiency profile than the qZSI.

It is important to note that the simulation results validate and verify the functionality and detailed comparative analysis and discussions of the presented inverters.

#### B. CASE-II: CLOSED-LOOP ANALYSIS

In this case study, the parameters of the grid-connected QBI system are summarized in Table 6. Fig. 20 shows the voltage and current responses of the system for a step decrease in the input current. It can be observed from Fig. 20 that, when the input current is reduced at the time 0.3 sec, the dc-link voltage decreases until the dc-link voltage controller acts to restore its value to the reference value by decreasing the d-axis current, and hence the line currents decrease.

Finally, the results of both case studies for steady-state and transient response in the closed-loop operation confirm the viability of the proposed QBI topology with the modulation and control scheme.

**FIGURE 18.** Simulated losses distribution in the 1 kVA three-phase QBI for B6 switches, input, and forward diodes, and passive components at full-load using PLECS.  $P_C$ : Power Loss in ESR of the capacitors,  $P_L$ : Power Loss in the inductors parasitic resistances,  $P_D$ : Loss in the diodes 1,2,3,  $P_{Df}$ : Loss in the forward diodes,  $P_{B6SW}$  and  $P_{B6C}$  are the switching and condition losses in the B6 switches.

FIGURE 19. Simulated efficiency of 1kVA QBI and qZSI.

TABLE 6. Parameters for closed-loop case study.

| Parameters            | Values | Parameters           | Values |

|-----------------------|--------|----------------------|--------|

| Filter inductance     | 7mH    | Filter resistance    | 2 Ω    |

| Ref. input current    | 10A    | Ref. dc-link voltage | 950V   |

| Parasitic Resistances | 0.12   | Input Voltage        | 100V   |

# **VII. EXPERIMENTAL RESULTS**

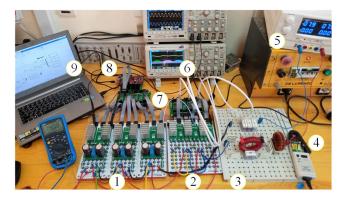

This section describes the experimental work and measurements taken on a downscaled QBI prototype, which is based on a custom-designed and configurable power electronics development kit from PEModule<sup>®</sup> [35]. The photograph of the experimental setup is shown in Fig. 21. The dc-side's passive elements are selected as in the simulation study, while the inverter output terminals are connected to a star-connected inductive load. The main system parameters are listed as follows:

- 1) The dc-side passive elements:  $L_1 = L_2 = 1.25$ mH,  $C_1 = C_2 = 120 \mu F$ .

- 2) The three-phase load:  $R = 10\Omega$ , L = 5mH.

- 3) The supply voltage: 15V.

- 4) Output voltage: 45V/Line at 50Hz.

- 5) Switching frequency: 10kHz.

The low-cost LAUNCHXL-F28379D development kit is used to implement the modulation strategy of the QBI to obtain an output line voltage of 45V at 50Hz. A deadtime of 5usec is inserted between the gating pulses. The experimental results

FIGURE 20. Simulated results for the closed-loop operation, the input current is reduced from 10A to 7.5A at 0.3 sec.

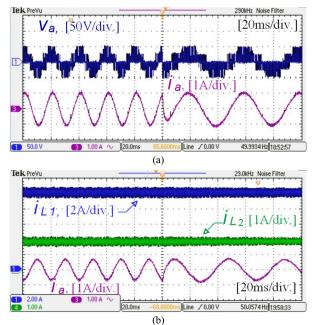

are captured by the DPO2024 Tektronics Oscilloscope, while the current sensors are used to measure the input, and output currents as well as the device's current stresses. The experimental results are shown in Figs. 22-28.

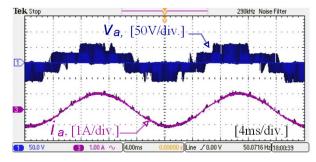

Fig. 22 shows the output voltage and current waveforms for the case study. The output current is near the sinusoidal waveform with low distortion, and the waveforms sound close to the theoretical.

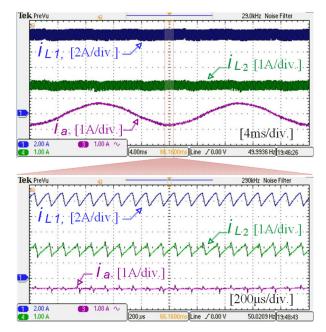

The inductor currents,  $i_{L1}$ ,  $i_{L2}$  and the load current waveforms are experimentally measured, and the results are shown in Fig. 23. As can be observed the current of the inductor  $L_1$  is larger than the inductor  $L_2$ , while both waveforms shed light on low-frequency components. This is owed to utilizing the MSVM schemes. Moreover, the zooming of the inductor currents is shown in Fig. 23, which illustrates the charging and discharging operations.

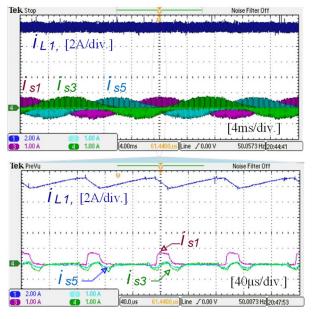

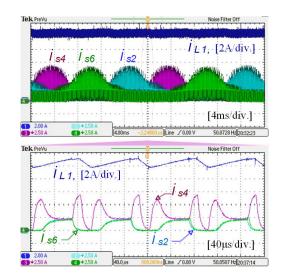

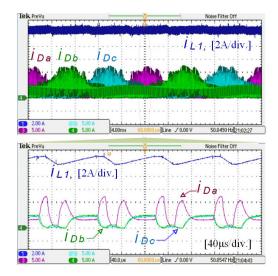

To confirm the theoretical study about the current stresses on the inverter devices, Figs. 24-26 show the current of inverter upper and lower switches as well as on the forward diodes.

It can be noticed from the results of Figs. 24-26 that; the experimental results confirm the theoretical study about the current stresses on the semiconductor devices. The lower switches and the forward diodes of the proposed topology suffer from higher current stresses than the upper switches of the inverter bridge. It is worth noting that in Figs. 24-26, the input current is displayed to show the current stresses during the charging and discharging intervals in the zooming figures.

To confirm the feasibility of using the proposed topology with the motor drive systems, Fig. 27 shows the experimental results of the output voltage, and current as well as the inductor currents for a step-change in the output frequency and output voltage. The frequency is changed in Fig. 27 from

# **IEEE**Access

FIGURE 21. Experimental Setup Photograph. ① Three-Phase Inverter bridge with Current Sensors, ② Forward diodes with Current sensors, ③ Impedance network, ④ Current probe, ⑤ Power supply, ⑥ Oscilloscope, ⑦ Current measurement boards, ⑧ LAUNCHXL-F28379D kit, ⑨ Laptop.

FIGURE 22. Experimental results for output phase voltage (upper trace, 50V/div.), current (lower trace, 2A/div).

FIGURE 23. Experimental results for the inductor currents and output phase current waveforms.

50Hz to 25Hz. As can be observed from the results, a smooth dynamic transition is achieved.

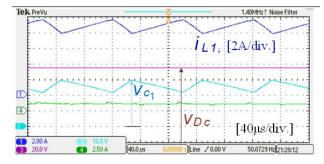

The capacitors voltages,  $v_{dc}$  and  $v_{c1}$  are experimentally measured and the results are shown in Fig. 28. The proposed QBI boosts the input voltage from 15V to 95V at the dc-link

FIGURE 24. Experimental results for the current stresses of the upper switches.

FIGURE 25. Experimental results for the current stresses of the lower switches.

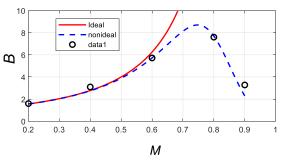

TABLE 7. Measured booting factor from the experimental results.

| М | 0.2  | 0.4  | 0.6  | 0.8 | 0.9  |

|---|------|------|------|-----|------|

| В | 1.51 | 2.64 | 4.72 | 5.6 | 2.28 |

(capacitor  $C_2$ ) while the average voltage across the capacitor  $C_1$  is lower with a value of 25V. It can be observed from Fig. 28 that, the trend of the capacitor voltage  $v_{c1}$  is opposite to that of the inductor current. This confirms the charging and discharging mode of operation of the proposed topology.

Table 7 lists the boosting factor of the experimental study versus the modulation index of the inverter under the same operating conditions. Fig. 29 shows a comparison between the experimental results and the results of the analytical study of the boosting factor of the QBI for ideal and non-ideal

FIGURE 27. Experimental results of a step change of the output frequency from 50Hz to 25Hz.

FIGURE 28. Experimental results of the capacitor voltage and input current of the proposed topology.

cases. it can be observed that a good agreement between the experimental and the analytical study is achieved.

FIGURE 29. Boosting factor versus the modulation index for both experimental and analytical study at the same operating conditions.

Finally, it can be mentioned that the presented theory, concepts, and analysis of the proposed QBI with the presented modulation scheme are confirmed using the simulation results given and the experimental work in this section.

#### **VIII. CONCLUSION**

In this paper, four modified Split Source Inverter (SSI) topologies with high voltage gains are proposed. These topologies square the boosting ability of the basic SSI. Therefore, it is called Quadratic-Boost Inverters (QBIs) in this paper. In all topologies, the dc-boosting factor and the ac-voltage gain are increased significantly by utilizing auxiliary inductors, capacitors, and diodes. In this paper, the modified SVM approach is selected to reduce the dc-side ripples. The steady-state and small-signal models of the analyzed topologies are introduced. Moreover, a closed-loop controller design guideline is presented. In addition, a comprehensive analysis and comparisons study with the conventional single-stage boosting inverter topologies such as SSI and qZSI are presented to bring out the merits of the proposed topologies. This analysis includes the boosting factor, output voltage gain, voltage, and current stresses on the semiconductors and passive components. Finally, the effectiveness of the proposed QBI architecture is verified via simulation and experimental results. According to this paper, it can be concluded that the proposed topologies are more suitable than the other counterparts (basic SSI and qZSI) for renewable energy applications and could be widely used for the PV and FC applications where high voltage gain is required from a low input voltage.

#### REFERENCES

- B. K. Hodge, Alternative Energy Systems and Applications. Hoboken, NJ, USA: Wiley, 2010.

- [2] A. A. Khodadoost Arani, G. B. Gharehpetian, and M. Abedi, "Review on energy storage systems control methods in microgrids," *Int. J. Electr. Power Energy Syst.*, vol. 107, pp. 745–757, May 2019.

- [3] M. Ahmed, M. Orabi, and O. AbdelRahim, "Two-stage micro-grid inverter with high-voltage gain for photovoltaic applications," *IET Power Electronics*, vol. 6, no. 9, pp. 1812–1821, Nov. 2013.

- [4] D. Debnath and K. Chatterjee, "Two-stage solar photovoltaic-based standalone scheme having battery as energy storage element for rural deployment," *IEEE Trans. Ind. Electron.*, vol. 62, no. 7, pp. 4148–4157, Jul. 2015.

- [5] M. Shayestegan, "Overview of grid-connected two-stage transformerless inverter design," J. Mod. Power Syst. Clean Energy, vol. 6, no. 4, pp. 642–655, Jul. 2018.

- [6] R. Dogga and M. K. Pathak, "Recent trends in solar PV inverter topologies," Sol. Energy, vol. 183, pp. 57–73, May 2019.

- [7] A. Mahmood, M. Zaid, S. Khan, M. Siddique, A. Iqbal, and Z. Sarwer, "A non-isolated quasi-Z-source-based high-gain DC–DC converter," *Int. J. Circuit Theory Appl.*, vol. 50, no. 2, pp. 653–682, 2021.

- [8] J. Ahmad, M. Zaid, A. Sarwar, M. Tariq, and Z. Sarwer, "A new transformerless quadratic boost converter with high voltage gain," *Smart Sci.*, vol. 8, no. 3, pp. 163–183, Jul. 2020, doi: 10.1080/23080477.2020.1807178.

- [9] R. Venkateswari and S. Sreejith, "Factors influencing the efficiency of photovoltaic system," *Renew. Sustain. Energy Rev.*, vol. 101, pp. 376–394, Mar. 2019.

- [10] F. Z. Peng, "Z-source inverter," *IEEE Trans. Ind. Appl.*, vol. 39, no. 2, pp. 504–510, Mar./Apr. 2003.

- [11] O. Ellabban and H. Abu-Rub, "Z-source inverter: Topology improvements review," *IEEE Ind. Electron. Mag.*, vol. 10, no. 1, pp. 6–24, Mar. 2016.

- [12] Y. P. Siwakoti, F. Z. Peng, F. Blaabjerg, P. C. Loh, and G. E. Town, "Impedance-source networks for electric power conversion Part I: A topological review," *IEEE Trans. Power Electron.*, vol. 30, no. 2, pp. 699–716, Feb. 2015.

- [13] Y. P. Siwakoti, F. Z. Peng, F. Blaabjerg, P. C. Loh, G. E. Town, and S. Yang, "Impedance-source networks for electric power conversion Part II: Review of control and modulation techniques," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 1887–1906, Apr. 2015.

- [14] A. Abdelhakim, F. Blaabjerg, and P. Mattavelli, "Modulation schemes of the three-phase impedance source inverters—Part I: Classification and review," *IEEE Trans. Ind. Electron.*, vol. 65, no. 8, pp. 6309–6320, Aug. 2018.

- [15] A. Abdelhakim, F. Blaabjerg, and P. Mattavelli, "Modulation schemes of the three-phase impedance source inverters—Part II: Comparative assessment," *IEEE Trans. Ind. Electron.*, vol. 65, no. 8, pp. 6321–6332, Aug. 2018.

- [16] S. M. Dabour, A. S. Abdel-Khalik, S. Ahmed, and A. M. Massoud, "A family of discontinuous PWM strategies for quasi Z-source nineswitch inverters," *IEEE Access*, vol. 9, pp. 169161–169176, 2021, doi: 10.1109/ACCESS.2021.3137541.

- [17] N. El-Hendawy, S. M. Dabour, and E. M. Rahsad, "Common-mode voltage analysis of three-phase quasi-Z source inverters for transformerless photovoltaic systems," in *Proc. IEEE Conf. Power Electron. Renew. Energy* (*CPERE*), Aswan, Egypt, Oct. 2019, pp. 355–360.

- [18] S. M. Dabour, A. S. Abdel-Khalik, S. Ahmed, and A. Massoud, "Carrierbased PWM strategy for quasi-Z source nine-switch inverters," in *Proc. IEEE Conf. Power Electron. Renew. Energy (CPERE)*, Aswan, Egypt, Oct. 2019, pp. 105–111.

- [19] R. Hammad, S. M. Dabour, and E. M. Rashad, "Open-circuit fault detection of asymmetrical six-phase induction motor fed from Z-source inverter," in *Proc. 21st Int. Middle East Power Syst. Conf. (MEPCON)*, Cairo, Egypt, Dec. 2019, pp. 1216–1222.

- [20] A. Abdelhakim, P. Mattavelli, and G. Spiazzi, "Three-phase split-source inverter (SSI): Analysis and modulation," *IEEE Trans. Power Electron.*, vol. 31, no. 11, pp. 7451–7461, Nov. 2016.

- [21] S. S. Lee and Y. E. Heng, "Improved single-phase split-source inverter with hybrid quasi-sinusoidal and constant PWM," *IEEE Trans. Ind. Electron.*, vol. 64, no. 3, pp. 2024–2031, Mar. 2017.

- [22] A. Abdelhakim, P. Mattavelli, P. Davari, and F. Blaabjerg, "Performance evaluation of the single-phase split-source inverter using an alternative DC-AC configuration," *IEEE Trans. Ind. Electron.*, vol. 65, no. 1, pp. 363–373, Jan. 2018.

- [23] S. S. Lee, A. S. T. Tan, D. Ishak, and R. Mohd-Mokhtar, "Single-phase simplified split-source inverter (S<sup>3</sup>I) for boost DC–AC power conversion," *IEEE Trans. Ind. Electron.*, vol. 66, no. 10, pp. 7643–7652, Oct. 2019.

- [24] C. Yin, Z. Xin, W. Ding, and P. C. Loh, "Modified split-source inverter with single-phase dual power decoupling," *IET Power Electron.*, vol. 13, no. 11, pp. 2201–2211, Aug. 2020.

- [25] S. M. Dabour, A. S. Abdel-Khalik, S. Ahmed, and A. Massoud, "An optimal PWM technique for dual-output nine-switch boost inverters with minimum passive component count," *IEEE Trans. Power Electron.*, vol. 36, no. 1, pp. 1065–1079, Jan. 2021.

- [26] M. K. Pinjala and R. Bhimasingu, "Improving the DC-link utilization of nine-switch boost inverter suitable for six-phase induction motor," *IEEE Trans. Transp. Electrific.*, vol. 6, no. 3, pp. 1177–1187, Sep. 2020.

- [27] A. Abdelhakim, P. Mattavelli, and G. Spiazzi, "Three-phase three-level flying capacitors split-source inverters: Analysis and modulation," *IEEE Trans. Ind. Electron.*, vol. 64, no. 6, pp. 4571–4580, Jun. 2017.

- [28] M. AbdulSalam, S. M. Dabour, and E. M. Rashad, "Cascaded multilevel split-source inverters: Analysis and modulation," in *Proc. 21st Int. Middle East Power Syst. Conf. (MEPCON)*, Cairo, Egypt, Dec. 2019, pp. 1204–1209.

- [29] M. Chen, C. Yin, L. Ming, and P. C. Loh, "A single-stage three-phase split-Y-source inverter," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Baltimore, MD, USA, Sep. 2019, pp. 2808–2813.

- [30] M. Chen, C. Yin, and P. C. Loh, "Magnetically coupled high-voltage-boost split Y-source inverter without leakage-induced voltage spikes," *IEEE Trans. Ind. Electron.*, vol. 67, no. 7, pp. 5444–5455, Jul. 2020.

- [31] F. Akbar, H. Cha, H. F. Ahmed, and A. A. Khan, "A family of single-stage high-gain dual-buck split-source inverters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 2, pp. 1701–1713, Jun. 2020.

- [32] O. Lopez-Santos, L. Martinez-Salamero, G. Garcia, H. Valderrama-Blavi, and T. Sierra-Polanco, "Robust sliding-mode control design for a voltage regulated quadratic boost converter," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 2313–2327, Apr. 2015.

- [33] A. Abdelhakim, P. Mattavelli, V. Boscaino, and G. Lullo, "Decoupled control scheme of grid-connected split-source inverters," *IEEE Trans. Ind. Electron.*, vol. 64, no. 8, pp. 6202–6211, Aug. 2017.

- [34] A. Abdelhakim, P. Davari, F. Blaabjerg, and P. Mattavelli, "Switching loss reduction in the three-phase quasi-Z-source inverters utilizing modified space vector modulation strategies," *IEEE Trans. Power Electron.*, vol. 33, no. 5, pp. 4045–4060, May 2018.

- [35] PEModule Technologies. Accessed: Dec. 31, 2021. [Online]. Available: https://www.pemodule.com

**SHERIF M. DABOUR** (Senior Member, IEEE) received the B.Sc. degree in electrical engineering from Zagazig University, Egypt, in 2002, and the M.Sc. and Ph.D. degrees in electrical power engineering from Tanta University, Egypt, in 2012 and 2015, respectively.

From 2003 to 2009, he was a Certified Trainer at Technical and Vocational Training Corporation, Riyadh, Saudi Arabia. Since 2009, he has been joined the Faculty of Engineering, Tanta Univer-

sity, where he is currently an Associate Professor (On-leave). Since 2022, he has been working as a Research Associate at Glasgow Caledonian University, U.K. Moreover, he is a reviewer for several journals, including IEEE TRANSACTION ON POWER ELECTRONICS, IEEE TRANSACTION ON INDUSTRIAL ELECTRONICS, *IET Power Applications*, and *IET Power Electronics*. He has been serving as a Treasurer for the IEEE Power Electronics Society (PELS) Egypt Chapter, from 2017 to 2020. His research interests include PWM techniques, power converters, electric drives, and renewable energy conversion systems.

**MAJED A. ALOTAIBI** (Member, IEEE) received the B.Sc. degree in electrical engineering from King Saud University, Riyadh, Saudi Arabia, in 2010, and the M.A.Sc. and Ph.D. degrees in electrical and computer engineering from the University of Waterloo, Waterloo, Canada, in 2014 and 2018, respectively.

He is currently an Assistant Professor with the Department of Electrical Engineering, King Saud University. He has worked as an Electrical Design

Engineer with ABB Saudi Arabia. His research interests include power system planning, operation, renewable energy modeling, applied optimization, and smart grid. He has served as a Reviewer for the IEEE TRANSACTIONS ON POWER SYSTEMS and the IEEE TRANSACTIONS ON SMART GRIDS.

**AMR A. ABD-ELAZIZ** was born in United Arab Emirates, in February 1996. He received the B.Sc. degree (Hons.) in electrical engineering from the Electrical Power and Machines Engineering Department, Tanta University, Tanta, Egypt, in 2019, where he is currently pursuing the M.Sc. degree in power electronics with a focus on modeling and control of grid-connected split-source inverter systems for photovoltaic applications.

Assistant with the Faculty of Engineering, Tanta University.

**MAHMOUD A. ALSHAHAT** (Student Member, IEEE) was born in Egypt, in July 1994. He received the B.Sc. degree (Hons.) in electrical engineering from the Electrical Power and Machines Engineering Department, Tanta University, Tanta, Egypt, in 2017, where he is currently pursuing the M.Sc. degree in power electronics with a focus on modeling and control of modular multilevel converters with energy storage systems for photovoltaic applications.

Since August 2017, he has been a Research Assistant with the Power Electronics and Electric Drives Research Laboratory, Tanta University, where he helped in implementing several power electronic converters for different research activities.

**MAHMOUD ABDALLAH** (Senior Member, IEEE) was born in Qena, Egypt, in 1974. He received the B.Sc. and M.Sc. degrees in electrical engineering from Minia University, Minya, Egypt, in 1997 and 2001, respectively, and the Ph.D. degree in electrical engineering from the Nagoya Institute of Technology, Nagoya, Japan, in 2010. Since 1999, he has been with the Department of Electrical Engineering, Faculty of Energy Engineering, Aswan University, Aswan, Egypt,

first as an Administrator, and since 2001, as a Lecturer. Since 2010, he has been with the Faculty of Engineering, South Valley University, Qena, first as an Assistant Professor and since 2015, as an Associate Professor. His research interests include voltage regulation and loss minimization of electrical distribution systems using series and shunt pulsewidth modulation (PWM) converters, PWM techniques for bidirectional AC/DC converters and direct AC/AC matrix converters, single-phase and three-phase multilevel converters, modular multilevel converters, battery chargers and regeneration circuits for electric vehicles (EVs), in addition to renewable energy applications and machine drives. He is a Senior Member of the IEEE Power Electronics and Industry Application Societies.

**ALI M. ELTAMALY** received the B.Sc. and M.Sc. degrees in electrical engineering from Al-Minia University, Egypt, in 1992 and 1996, respectively, and the Ph.D. degree in electrical engineering from Texas A&M University, in 2000. He is currently a Full Professor with King Saud University, Saudi Arabia, and Mansoura University, Egypt. He has published 15 books and book chapters. He has authored or coauthored more than 200 refereed journal articles and conference papers, and a num-

ber of patents with the U.S. Patent Office. He has supervised several M.Sc. and Ph.D. theses and worked on number of technical projects. His current

research interests include renewable energy, smart grids, power electronics, motor drives, power quality, artificial intelligence, evolutionary and heuristic optimization techniques, and distributed generation. He received the Professor Award for Scientific Excellence from the Egyptian Supreme Council of Universities, Egypt, in June 2017, and has been awarded many prizes from different universities in Egypt and Saudi Arabia. He has chaired many international conference sessions. He participates as an editor and an associate editor for many international journals.

**AYMAN S. ABDEL-KHALIK** (Senior Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from Alexandria University, Alexandria, Egypt, in 2001 and 2004, respectively, and the joint Ph.D. degree in electrical engineering from Alexandria University, and Strathclyde University, Glasgow, U.K., in 2009, under a dual channel program. He is currently a Professor with the Electrical Engineering Department, Faculty of Engineering, Alexandria University. He serves as

the Editor-in-Chief for *Alexandria Engineering Journal*. He also serves as an Associate Editor for IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS and *IET Electric Power Applications* journal. His current research interests include electrical machine design and modelling, electric drives, energy conversion, and renewable energy.

AHMED M. MASSOUD (Senior Member, IEEE) received the B.Sc. (Hons.) and M.Sc. degrees in electrical engineering from Alexandria University, Egypt, in 1997 and 2000, respectively, and the Ph.D. degree in electrical engineering from Heriot-Watt University, Edinburgh, U.K., in 2004. He is currently an Associate Dean for Research and Graduate Studies and a Full Professor with the Department of Electrical Engineering, College of Engineering, Qatar University. He holds five U.S.

patents. He published more than 100 journal articles in the fields of power electronics, energy conversion, and power quality. His research interests include power electronics, energy conversion, renewable energy, and power quality.

**SHEHAB AHMED** (Senior Member, IEEE) received the B.Sc. degree from Alexandria University, in 1999, and the M.Sc. and Ph.D. degrees from Texas A&M University, College Station, in 2000 and 2007, respectively. He was with Schlumberger Technology Corporation, Houston, TX, USA, from 2001 to 2007, developing downhole mechatronic systems for oilfield service products. He was with Texas A&M University at Qatar, from 2007 to 2018. He is currently a Professor and

the Chair of the Electrical and Computer Engineering Program within the CEMSE Division, King Abdullah University of Science and Technology, Saudi Arabia. His research interests include subsurface mechatronics, solid-state power conversion, electric machines, and drives.

...