## **QATAR UNIVERSITY**

#### COLLEGE OF ENGINEERING

# DESIGN OF PMU BASED REAL TIME FUZZY LOGIC SVC DAMPING CONTROLLER TO ENHANCE INTER- AREA OSCILLATION DAMPING

BY

#### SAMI SULIMAN ABUEIDA

A Thesis Submitted to the Faculty of

College of Engineering

in Partial Fulfillment

of the Requirements

for the Degree of

Master of Science in

**Electrical Engineering**

June 2016

©2016 Sami Suliman Abueida. All Rights Reserved.

# **COMMITTEE PAGE**

The members of the Committee approve the thesis of **Sami Suliman Abueida** defended on 17 May 2016.

|                                | Dr. Uvais Ahmed Qidwai            |

|--------------------------------|-----------------------------------|

|                                | Thesis/Dissertation Supervisor    |

|                                | Dr. Khaled Ellithy                |

|                                | Thesis/Dissertation Co-Supervisor |

|                                | Dr. Khaled El-Metwally            |

|                                | Committee Member                  |

|                                | Dr. Nader Meskin                  |

|                                | Committee Member                  |

|                                | Dr. Hasan Mehrjerdi               |

|                                | Committee Member                  |

|                                |                                   |

| Approved:                      |                                   |

|                                |                                   |

| Dr. Khalifa Nasser Al-Khalifa, | Dean, College of Engineering      |

#### **Abstract**

Inter-area oscillation has been identified as a significant problem in the utility systems due to the damages that it may cause as well as the limitation introduced to power transfer capability. A contemporary solution to this issue is by adding power system stabilizer (PSS) to the generator's automatic voltage regulator (AVR). Although nowadays most of the generators are equipped with conventional PSSs, their effects are only noticed on the damping of local oscillations and they do not contribute effectively on damping the inter-area oscillations. Adding auxiliary signals (stabilizing signals) to Flexible AC Transmission System (FACTS) device such as Static VAr Compensator (SVC)&Static Synchronous Compensator (STATCOM) would help in extending the power transfer capability and enhancing the voltage. The stabilizing signals can be derived from damping controller. In this thesis, a Phasor Measurement Unit (PMU) based real-time, Hardware in the Loop, fuzzy logic shunt FACTS controller is proposed to ensure a satisfactory damping of inter-area oscillations which will enhance system stability and increase power transfer capability.

The concerned power system has been modeled using Real-Time Digital Simulator (RTDS), where the designed Hardware-in-the-loop damping controller was tested for the sake of evaluating the effectiveness of the proposed controller in enhancing the damping of inter-area oscillations. Time-domain simulations results have shown that the designed Fuzzy damping controller enhance the damping of inter-area oscillations of interconnected power system. This study is aimed to analyze the potential applications of PMU in the interconnected power systems of GCC smart

power grid. These systems are expected to face a stability problem of the inter-area mode of oscillations due to the weak tie-lines that connect the systems.

# **Table of Contents**

| TABLE OF  | F CONTENTS                                       | V   |

|-----------|--------------------------------------------------|-----|

| LIST OF A | BBREVIATION                                      | XIV |

| ACKNOW    | /LEDGEMENTS                                      | XVI |

| CHAPTER   | 1. INTRODUCTION                                  | 1   |

| 1.1.      | Power System Stability                           | 1   |

| 1.2.      | LOW FREQUENCY OSCILLATIONS (LFO)                 | 3   |

| 1.3.      | Inter-area Oscillations                          | 3   |

| 1.4.      | FLEXIBLE AC TRANSMISSION SYSTEM DEVICES (FACTS)  | 4   |

| 1.5.      | STATIC VAR COMPENSATOR                           | 6   |

| 1.6.      | PHAROS MEASUREMENT UNIT (PMU)                    | 10  |

| 1.7.      | PROBLEM STATEMENT                                | 12  |

| 1.8.      | OBJECTIVES OF THE WORK                           | 13  |

| 1.9.      | THESIS STRUCTURE                                 | 14  |

| CHAPTER   | 2. LITERATURE REVIEW                             | 16  |

| 2.1.      | FACTS Devices In Damping Inter-Area Oscillation  | 16  |

| 2.2.      | LOCAL AND WAMS IN DAMPING CONTROLLERS            | 17  |

| 2.3.      | WAMS & PMUS BASED DAMPING CONTROLLERS            | 18  |

| 2.4.      | ROBUST CONTROLLER                                | 19  |

| 2.5.      | CLASSICAL FUZZY DAMPING CONTROLLER               | 19  |

| 2.6.      | ADAPTIVE FUZZY DAMPING CONTROLLER                | 19  |

| 2.7.      | OUR CONTRIBUTION                                 | 22  |

| CHAPTER   | 3. POWER SYSTEM MODELING                         | 23  |

| 3.1.      | GENERATOR MODEL                                  | 23  |

| 3.2.      | EXCITATION SYSTEM MODELS                         | 24  |

| 3.3.      | POWER SYSTEM STABILIZER                          | 25  |

| 3.4.      | STATIC VAR COMPENSATORS                          | 26  |

| 3.5.      | TESTING SYSTEM                                   | 28  |

| CHAPTER   | 4. DESIGN OF FUZZY LOGIC DAMPING CONTROLLER      | 32  |

| 4.1.      | Introduction                                     | 32  |

| 4.2.      | FUZZY LOGIC CONTROLLER (FLC)                     | 33  |

| 4.2.      | 1 Fuzzification Stage:                           | 34  |

| 4.2.      | 2 The Rule / Knowledge Base                      | 36  |

| 4.2       | 3 Inference Engine / Mechanism                   | 36  |

| 4.2.      | 4 De-Fuzzification                               | 38  |

| 4.3.      | DESIGN OF FUZZY LOGIC DAMPING CONTROLLER FOR SVC |     |

| 4.3.      | 1 Choosing The Controller Inputs                 | 40  |

| 4.3       | 2 Choosing The Membership Functions Limits:      | 41  |

| 4.3       | 3 Fuzzification Stage                            | 41  |

| 43.       | 4 Inference Figure & Rule Rase                   | 42  |

| 4.3.5      | De-Fuzzification                                                          | 43           |

|------------|---------------------------------------------------------------------------|--------------|

| 4.3.6      | Controller Tuning (Choosing Gain's Values Ge, Gce & Go)                   | 43           |

| 4.3.7      | Online Adaptation Mechanism For The Fuzzy Logic controller                | 44           |

| CHAPTER 5. | SIMULATIONS AND RESULTS                                                   | 50           |

| 5.1. N     | AATLAB/ SIMULINK                                                          | 50           |

| 5.2. F     | TDS Model                                                                 | 55           |

| CHAPTER 6. | FLC HARDWARE IMPLEMENTATION                                               | 83           |

| 6.1. F     | LC PLATFORM PREPARATION                                                   | 83           |

| 6.1.1.     | Microcontroller Choosing                                                  | 84           |

| 6.1.2.     | Interface Peripherals (Uni-Polar To Bi-Polar & Bi-Polar To Uni-Polar)     | 85           |

| 6.1.3.     | Data Pre-Processing (Moving Average Filter)                               |              |

| 6.1.4.     | Microcontroller programming                                               | 90           |

| 6.2. F     | UZZY CONTROLLER DESIGN HELPER TOOL (FCDHT)                                | 91           |

| 6.2.1.     | Controller Developing Side                                                | 92           |

| 6.2.2.     | Microcontroller Programming Side                                          | 94           |

| 6.2.3.     | Main Structure                                                            | 94           |

| 6.3. II    | MPLEMENTATION RESULTS:                                                    | 98           |

| 6.3.1.     | Without the presence of any PSS                                           | 99           |

| 6.3.2.     | With The Presence Of All PSS, All PSS &SVC, And All PSS &SVC &Damping 101 | ζ Controller |

| CHAPTER 7. | CONCLUSION& FUTURE WORK                                                   | 106          |

| 7.1.       | Conclusion                                                                | 106          |

| 7.2. F     | UTURE WORK:                                                               | 108          |

| REFERENCE  | s                                                                         | 109          |

| APPENDIX-  | A SCHEMATICS & PCBS                                                       | 116          |

| APPENDIX-I | 3 TESTED RULE BASES                                                       | 118          |

| APPENDIX-0 | C TESTED MF LIMITS                                                        | 121          |

| APPENDIX-I | O MICROCONTROLLER CODE                                                    | 127          |

| APPENDIX-I | O RTDS FUZZY MODEL CODE                                                   | 134          |

| APPENDIX-I | E RTDS MODEL                                                              | 140          |

# List of Tables

| TABLE 2.1SUMMARY OF 2.1 AND 2.2                                                | 17 |

|--------------------------------------------------------------------------------|----|

| TABLE 2.2 SUMMARY OF 2.3                                                       | 18 |

| Table 2.3 Summary of 2.6                                                       | 21 |

| TABLE 3.1 TYPICAL VALUES OF SVC CONTROLLER [51]                                | 28 |

| TABLE3.2 TRANSFORMER PARAMETERS[49]                                            | 29 |

| Table 3.3 Branches Parameters [49]                                             | 29 |

| Table3.4 Load Flow Data [49]                                                   | 30 |

| Table3.5Loads [49]                                                             | 30 |

| Table 3.6 Generator Parameters [49]                                            | 30 |

| Table 3.7 Exciter & PSS Parameters [49]                                        | 31 |

| TABLE3.8SVC PARAMETERS                                                         | 31 |

| Table4.1 Linguistic Variables                                                  | 42 |

| Table 4.2 Main Controller Rule Base                                            | 43 |

| Table4.3 Loading Cases                                                         | 45 |

| TABLE4.4 RULE BASE OF THE SECOND FUZZY CONTROLLER                              | 48 |

| Table 5.1 Controller Input Combination                                         | 66 |

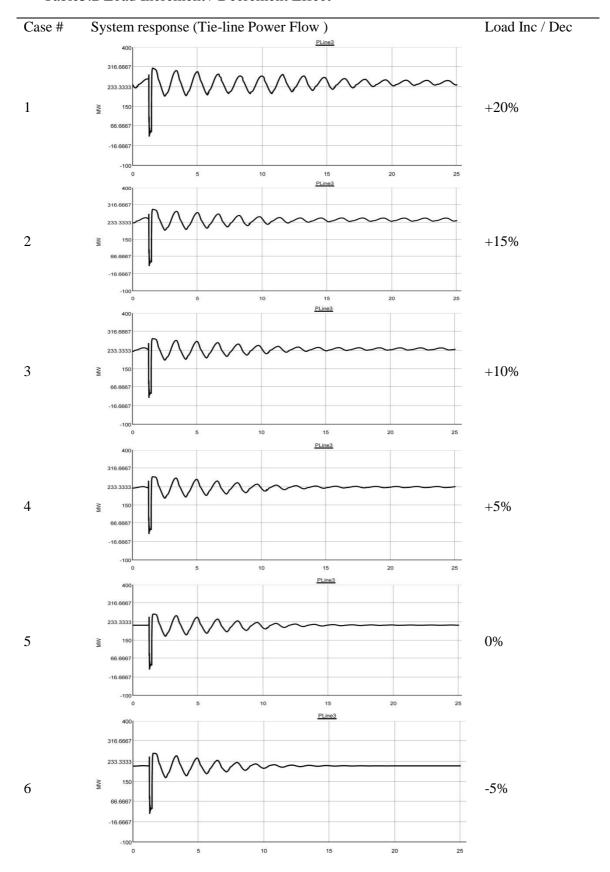

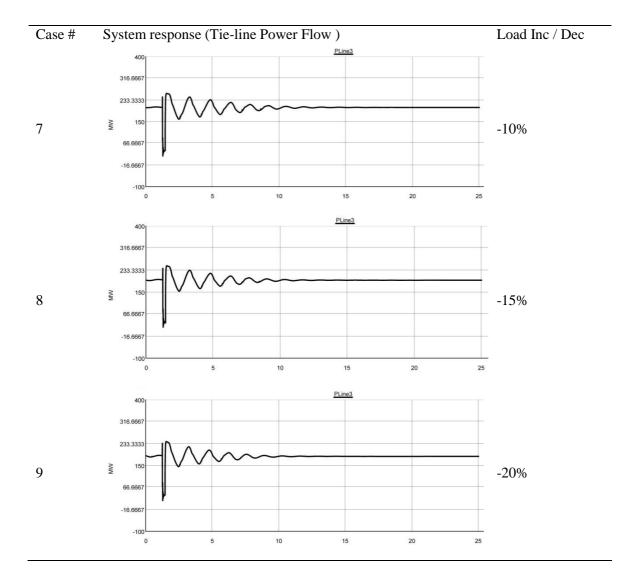

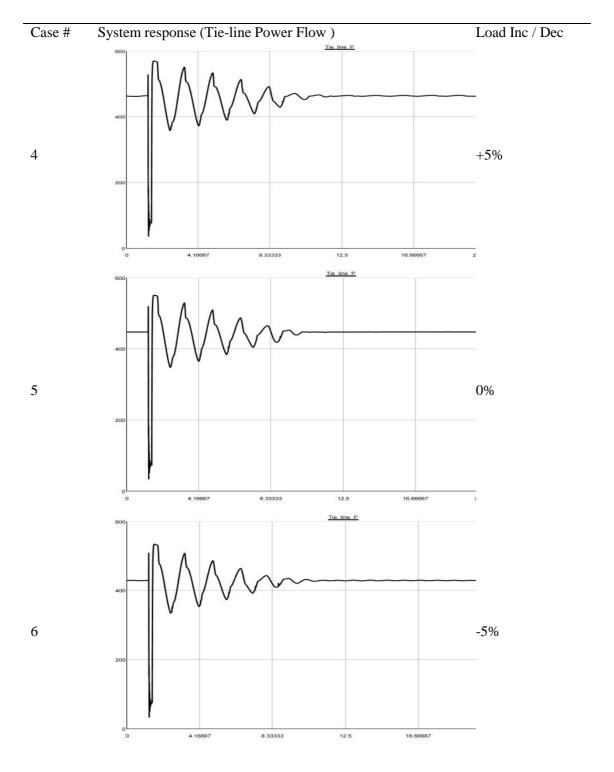

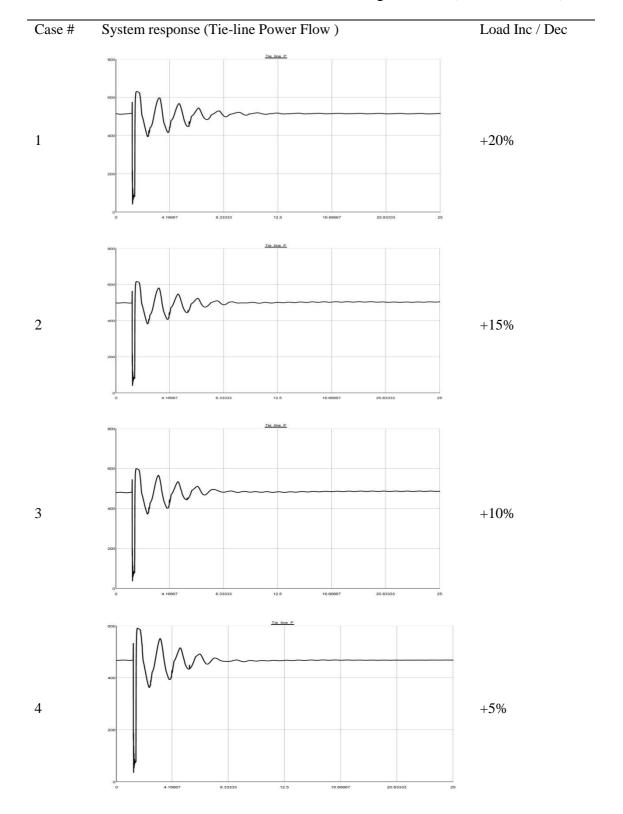

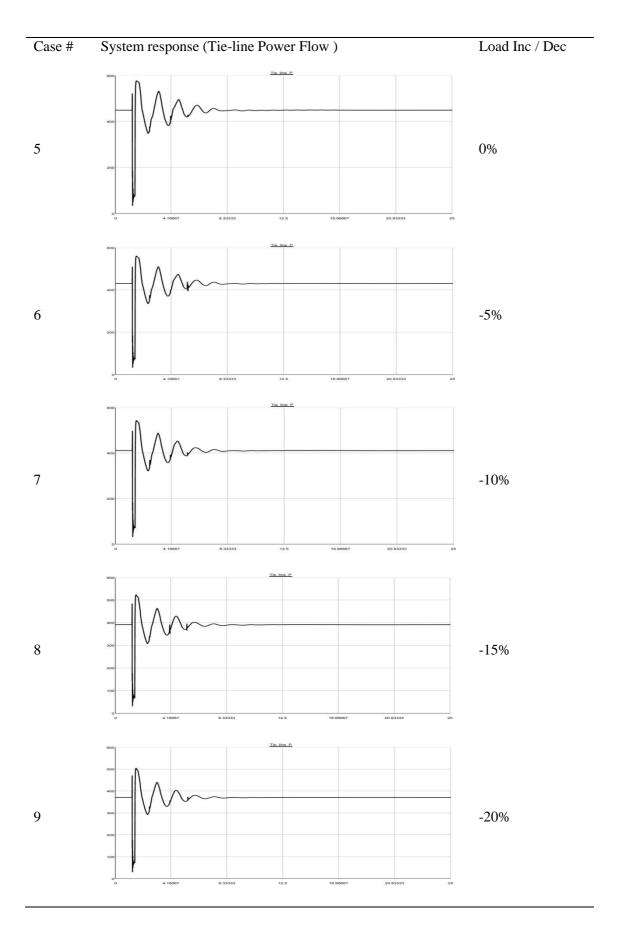

| Table 5.2 Load Increment / Decrement Effect                                    | 71 |

| TABLE 5.3 THE EFFECT OF ADDING ADAPTIVE CONTROLLER                             | 73 |

| TABLE 5.4 SETTLING TIME WITH AND WITHOUT THE PRESENCE OF ADAPTATION MECHANISM  | 76 |

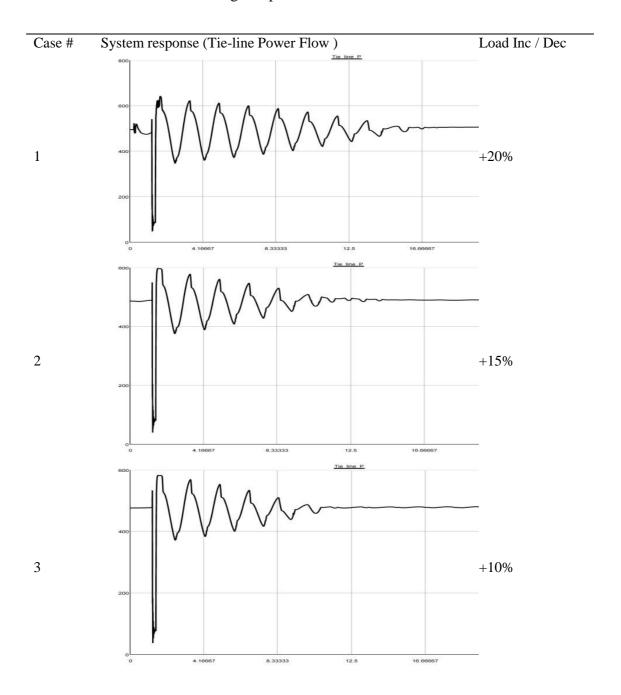

| TABLE 5.5 POWER AT THE TIE-LINE WITH DIFFERENT LOADING SCENARIOS (200MVAR SVC) | 79 |

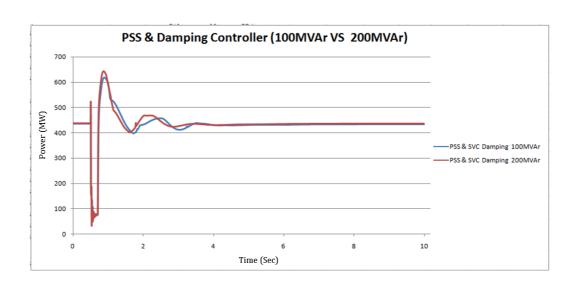

| TABLE 5.6 SETTLING TIME WITH100MVAR & 200MVAR SVC                              | 81 |

| TABLE 6.1 MICROCONTROLLERS FEATURES & COMPARISON                               | 85 |

| ΓABLE6.2 SAMPLE OF RULE BASE TABLE           | 93  |

|----------------------------------------------|-----|

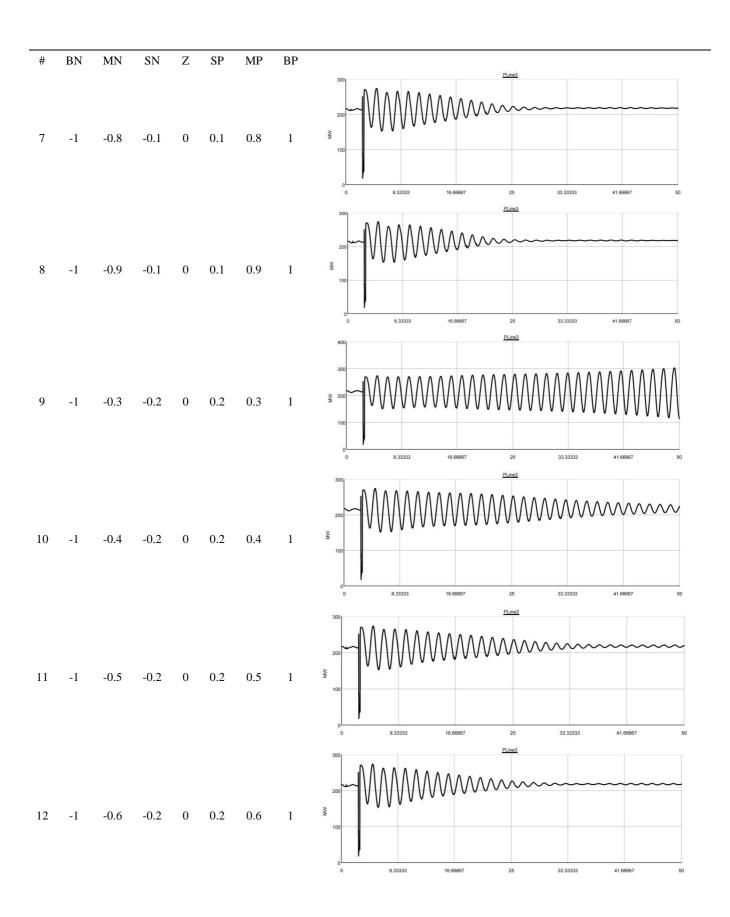

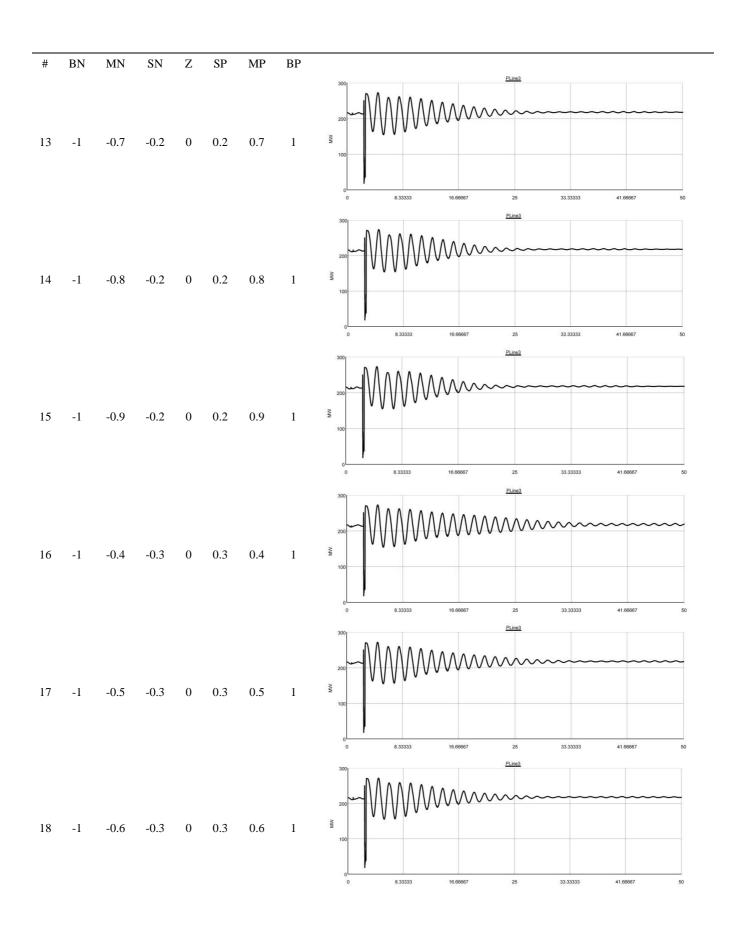

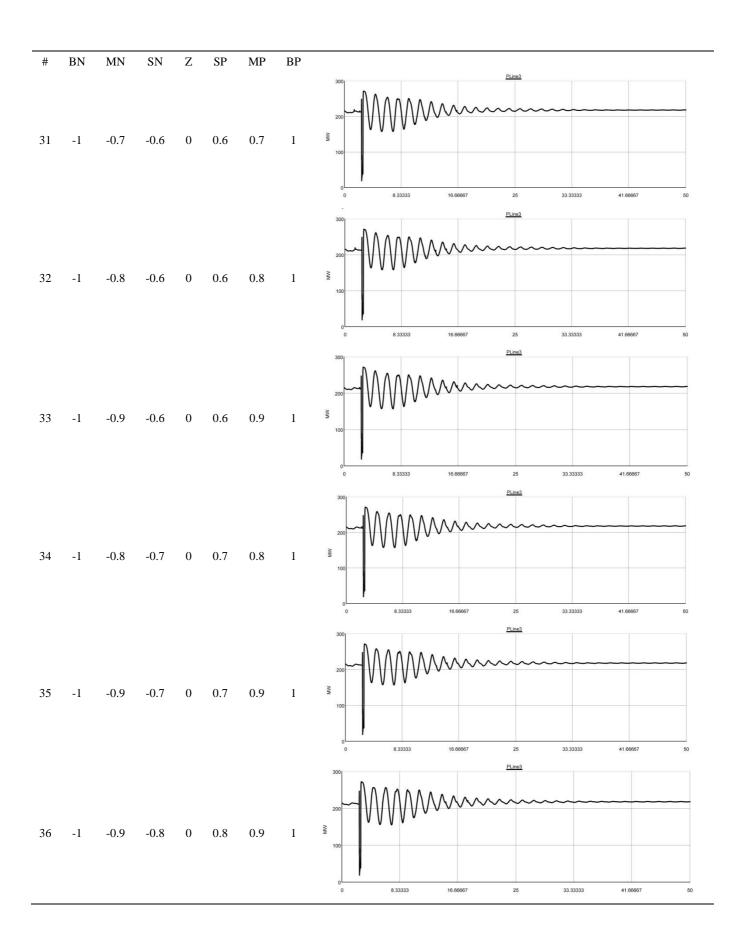

| ΓABLE 10.1 MEMBERSHIP FUNCTION TESTED LIMITS | 121 |

# List of Figures

| FIGURE 1.1GCC INTERCONNECTION DISTANCES & CAPACITIES [3] | 2  |

|----------------------------------------------------------|----|

| FIGURE 1.2 THE BASIC DIAGRAM OF THE SVC                  | 6  |

| FIGURE 1.3 V-I CHARACTERISTIC OF SVC                     | 7  |

| FIGURE 1.4 SVC CONTROL SYSTEM [11]                       | 8  |

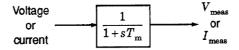

| FIGURE 1.5 MEASUREMENT MODULE [11]                       | 9  |

| FIGURE 1.6 VOLTAGE REGULATOR MODEL [10]                  | 9  |

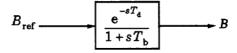

| FIGURE 1.7 THYRISTOR SUSCEPTANCE CONTROL [10]            | 10 |

| FIGURE 1.8 WAMS & PMU IN QU                              | 11 |

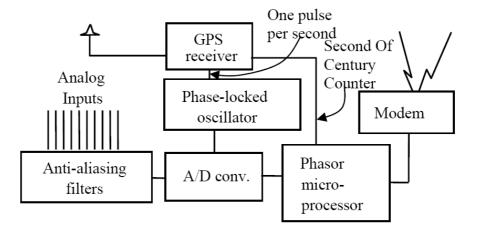

| FIGURE 1.9 PMU BLOCKS DIAGRAM [14]                       | 12 |

| FIGURE 3.1 EXCITER MODEL STATIC EXCITER [51]             | 25 |

| FIGURE 3.2 PSS MODEL                                     | 26 |

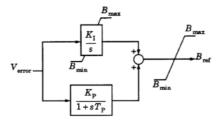

| FIGURE 3.3 SVC BASIC BLOCK DIAGRAM OF SVC MODEL [54]     | 27 |

| FIGURE 3.4 TESTING SYSTEM [51]                           | 28 |

| FIGURE 4.1 FLC STAGES                                    | 33 |

| FIGURE 4.2TRIANGLE MEMBERSHIP FUNCTION                   | 34 |

| FIGURE 4.3 TRAPEZOIDAL MEMBERSHIP FUNCTION               | 35 |

| FIGURE 4.4 GAUSSIAN MEMBERSHIP FUNCTION                  | 35 |

| FIGURE 4.5 GENERALIZED BILL MEMBERSHIP FUNCTION          | 35 |

| FIGURE 4.6 SIGMOID MEMBERSHIP FUNCTION                   | 36 |

| FIGURE 4.7 MAMDANI INFERENCE SYSTEM                      | 37 |

| FIGURE 4.8 CENTER OF GRAVITY                             | 38 |

| FIGURE 4.0 WEIGHTED AVERAGE                              | 20 |

| FIGURE 4.10 MEAN OF MAXIMUM                                                        | 40         |

|------------------------------------------------------------------------------------|------------|

| FIGURE 4.11 DAMPING CONTROLLER STRUCTURE                                           | 40         |

| FIGURE 4.12 TRIANGLE MEMBERSHIP FUNCTION                                           | 41         |

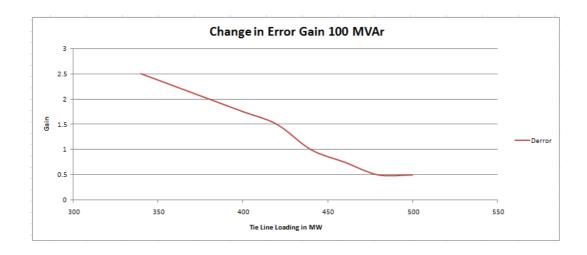

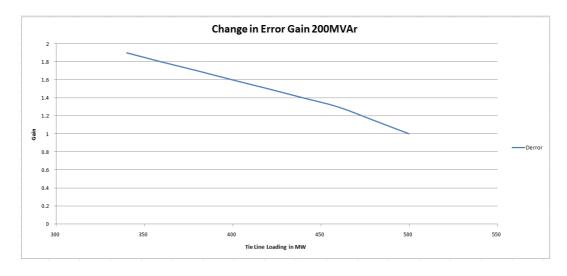

| FIGURE 4.13 CHANGE IN ERROR GAIN CURVE (100MVAR SVC)                               | 46         |

| FIGURE4.14 CHANGE IN ERROR GAIN CURVE (200MVAR SVC)                                | 46         |

| FIGURE 4.15 FLC CONTROLLER WITH THE ADAPTATION MECHANISM                           | 48         |

| FIGURE 4.16 INPUTS & OUTPUT MEMBERSHIP FUNCTION                                    | 49         |

| FIGURE 5.1 MATLAB MODEL OF TWO AREAS AND FOUR MACHINES                             | 51         |

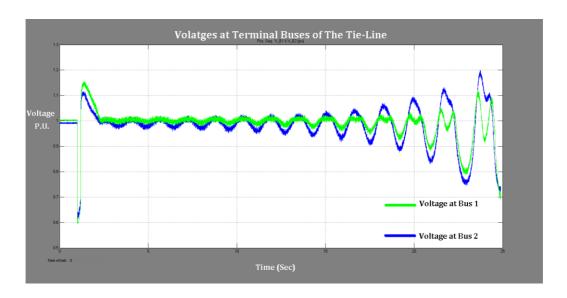

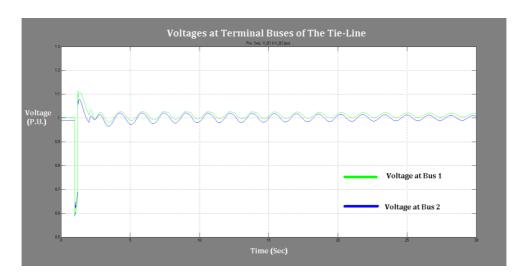

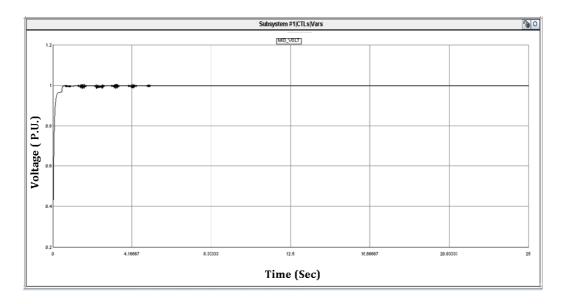

| FIGURE 5.2 TIE-LINE TERMINAL VOLTAGES, TIME RESPONSE UNDER 200 MS FAULT @ BUS 3 (I | No PSS) 52 |

| FIGURE 5.3 TIE-LINE POWER, TIME RESPONSE UNDER 200 MS FAULT @ BUS 3 (NO PSS)       | 52         |

| FIGURE 5.4 TIE-LINE TERMINAL VOLTAGES, TIME RESPONSE UNDER 200 MS FAULT @ BUS 3 (  | (No PSS,   |

| WITH SVC)                                                                          | 53         |

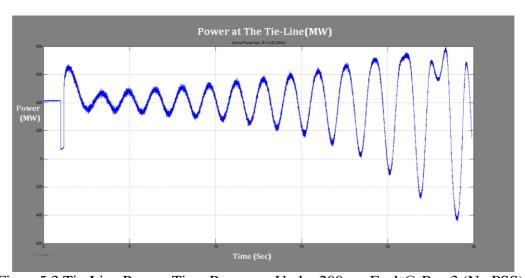

| FIGURE 5.5 TIE-LINE POWER, TIME RESPONSE UNDER 200 MS FAULT @ BUS 3 (NO PSS, WITH  | SVC)53     |

| Figure5.6Tie-Line Terminal Voltages, Time Response Under 200 ms Fault @ Bus 3 (    | (No PSS,   |

| WITH SVC &FL DAMPING CONTROLLER)                                                   | 54         |

| FIGURE 5.7 TIE-LINE POWER, TIME RESPONSE UNDER 200 MS FAULT @ BUS 3 (NO PSS, WITH  | SVC &FL    |

| DAMPING CONTROLLER)                                                                | 54         |

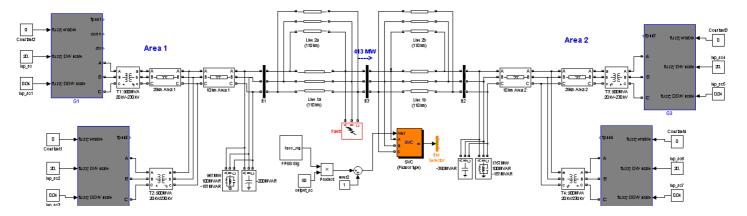

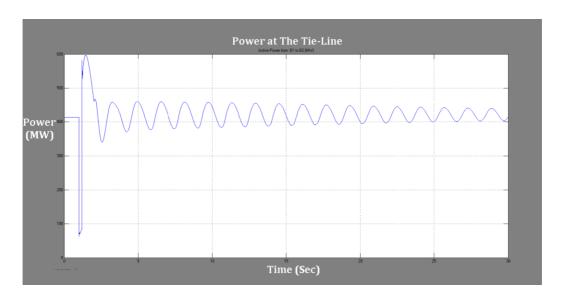

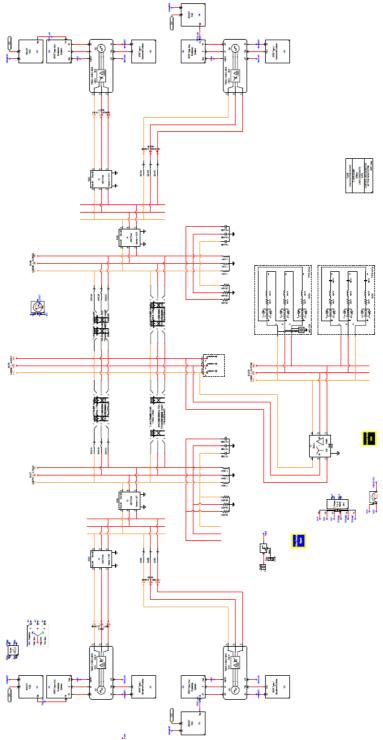

| Figure 5.8 RTDS Model                                                              | 56         |

| Figure 5.9RTDS Fuzzy Model                                                         | 57         |

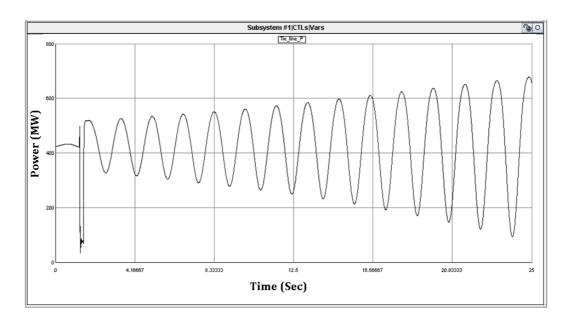

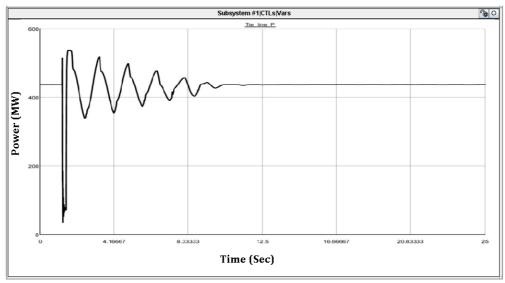

| FIGURE 5.10TIE-LINE POWER, TIME RESPONSE WITHOUT FAULT & NO PSS (INTER-AREA OSC    | CILLATION  |

| PHENOMENA)                                                                         | 58         |

| FIGURE 5.11TIE-LINE VOLTAGE (MIDPOINT), TIME RESPONSE WITHOUT FAULT & NO PSS (IN   | TER-AREA   |

| OSCILLATION PHENOMENA)                                                             | 58         |

| FIGURE 5.12 TIE-LINE POWER, TIME RESPONSE WITHOUT FAULT, NO PSS, WITH SVC ONLY (I  | NTER-      |

| AREA OSCILLATION PHENOMENA)                                                        | 59         |

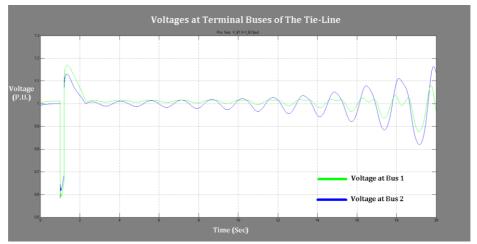

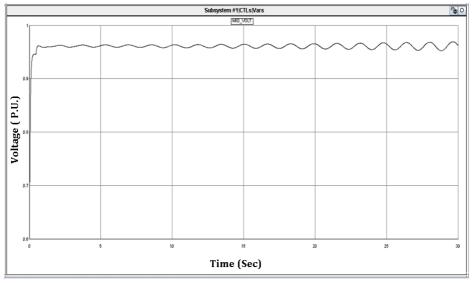

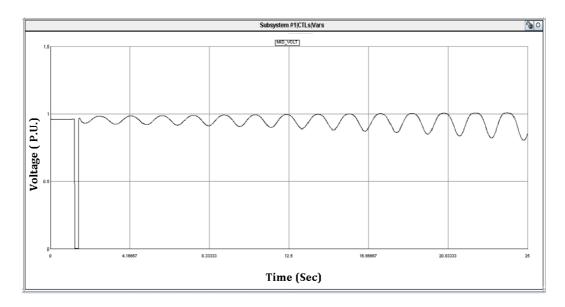

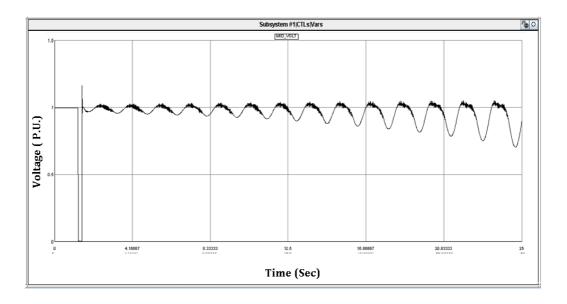

| FIGURE 5.13 TIE-LINE VOLTAGE (MIDPOINT), TIME RESPONSE WITHOUT FAULT, NO PSS, WITH SVC     |

|--------------------------------------------------------------------------------------------|

| ONLY (INTER-AREA OSCILLATION                                                               |

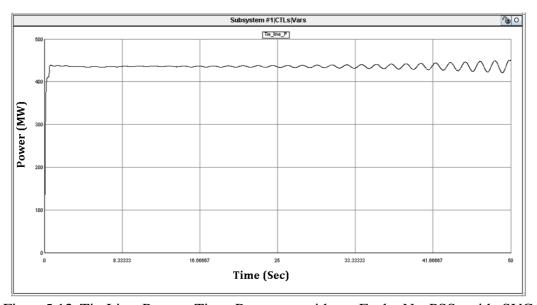

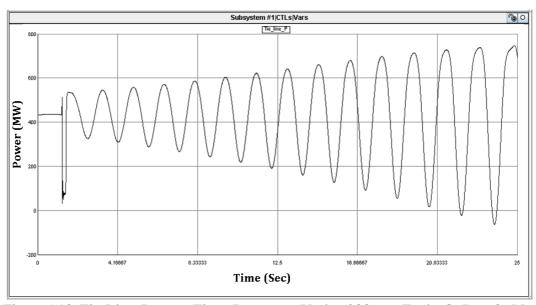

| FIGURE 5.14 TIE-LINE POWER, TIME RESPONSE WITHOUT FAULT, NO PSS, WITH SVC &FL DAMPING      |

| CONTROLLER (INTER-AREA OSCILLATION PHENOMENA)                                              |

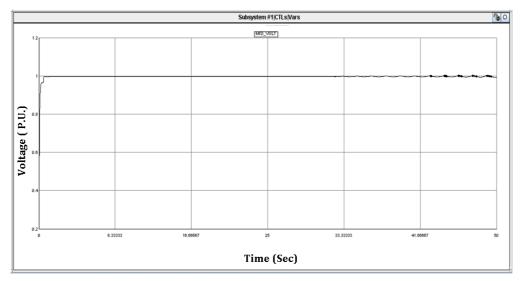

| FIGURE 5.15 TIE-LINE VOLTAGE (MIDPOINT), TIME RESPONSE WITHOUT FAULT, NO PSS, WITH SVC &FL |

| DAMPING CONTROLLER (INTER-AREA OSCILLATION PHENOMENA)                                      |

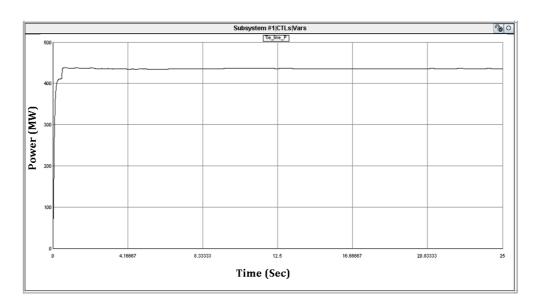

| FIGURE 5.16 TIE-LINE POWER, TIME RESPONSE UNDER 200 MS FAULT @ BUS 8 (NO PSS)              |

| FIGURE 5.17 TIE-LINE MIDPOINT VOLTAGES, TIME RESPONSE UNDER 200 MS FAULT @ BUS 8 (NO PSS)  |

| 63                                                                                         |

| FIGURE 5.18 TIE-LINE POWER, TIME RESPONSE UNDER 200 MS FAULT @ BUS 8 (NO PSS, WITH SVC).64 |

| FIGURE 5.19TIE-LINE MIDPOINT VOLTAGES, TIME RESPONSE UNDER 200 MS FAULT @ BUS 8 (NO PSS,   |

| WITH SVC)65                                                                                |

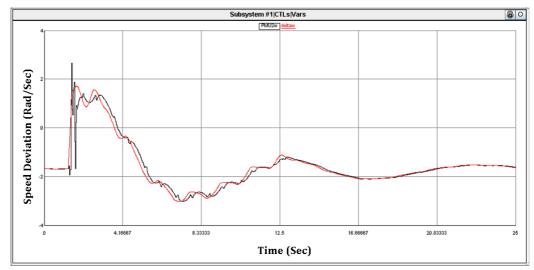

| FIGURE 5.20 PMU MEASURED SIGNAL VS GEN. 1 MEASURED SIGNAL                                  |

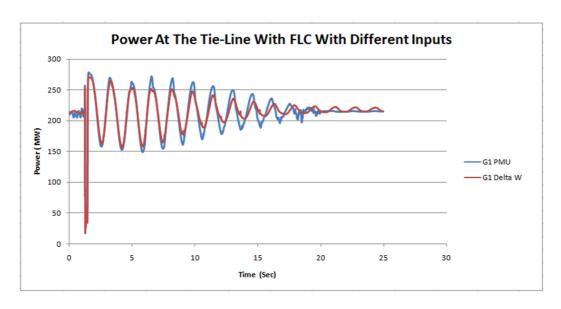

| FIGURE 5.21 TIE-LINE POWER, TIME RESPONSE USING DIFFERENT INPUTS MEASURED AT GEN 1         |

| TERMINAL UNDER FAULT CONDITIONS                                                            |

| FIGURE 5.22 TIE-LINE POWER, TIME RESPONSE USING (G1-G3) AS SIGNAL UNDER FAULT CONDITION 69 |

| FIGURE 5.23 TIE-LINE MIDPOINT VOLTAGES, TIME RESPONSE USING (G1-G3) SIGNAL UNDER FAULT     |

| CONDITION69                                                                                |

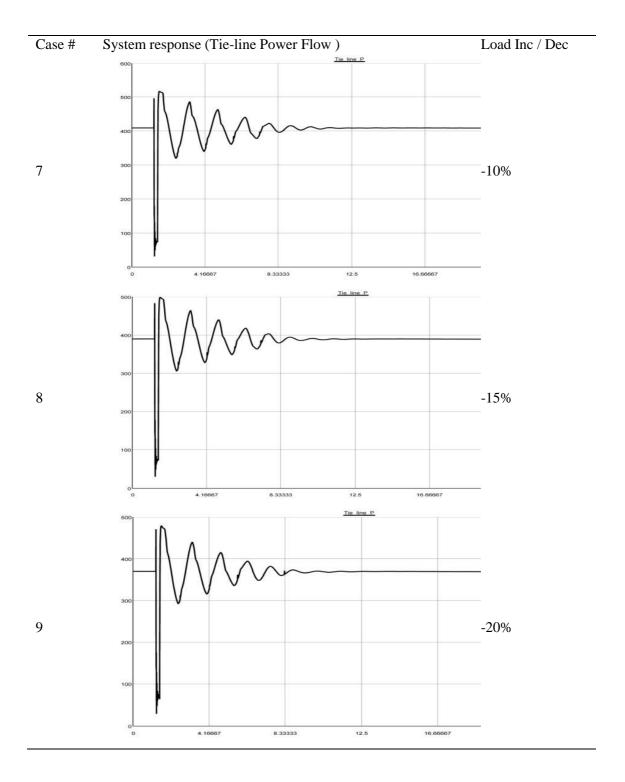

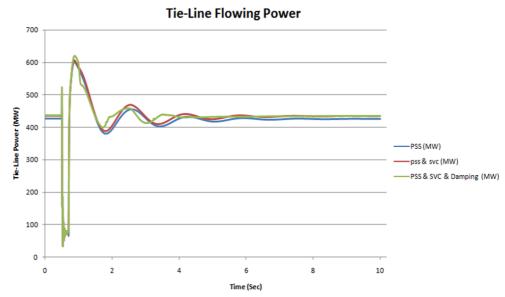

| FIGURE 5.24 DAMPING CONTROLLER PERFORMANCE COMPARED TO OTHER SCENARIOS (POWER)77           |

| FIGURE 5.25 DAMPING CONTROLLER PERFORMANCE COMPARED TO OTHER SCENARIOS (VOLTAGES).77       |

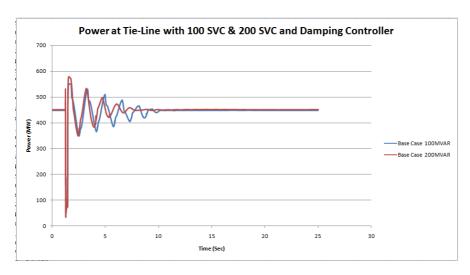

| FIGURE 5.26 THE EFFECT OF INCREASING THE SVC CAPACITY FROM 100 MVAR TO 200 MVAR78          |

| FIGURE 5.27 THE EFFECT OF USING 100MVAR AND 200MVAR ON POWER FLOWING THROUGH THE TIE-      |

| LINE DURING THE THREE PHASE SHORT CIRCUIT                                                  |

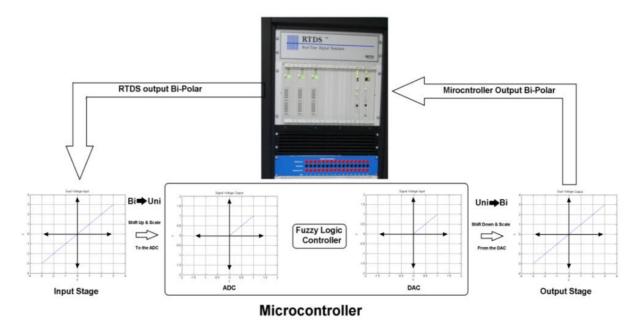

| FIGURE 6.1 THE FLC PLATFORM84                                                              |

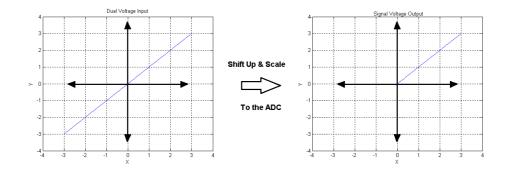

| FIGURE 6.2 BIPOLAR TO UNIPOLAR                                                             |

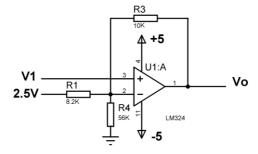

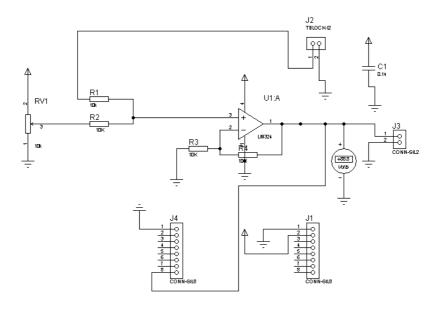

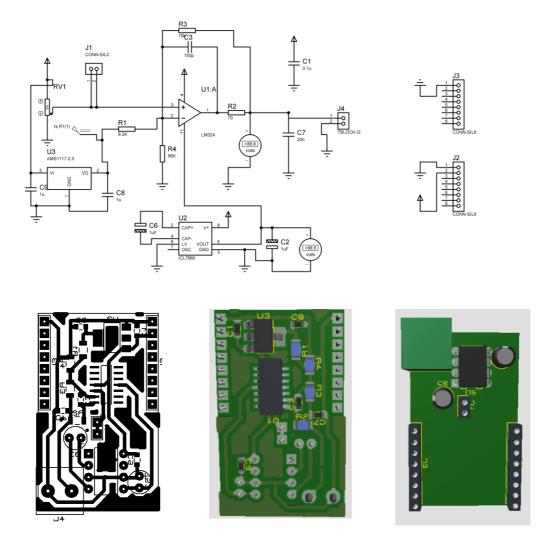

| FIGURE 6.3 CORE SCHEMATIC                                                          | 86       |

|------------------------------------------------------------------------------------|----------|

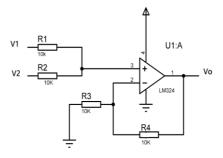

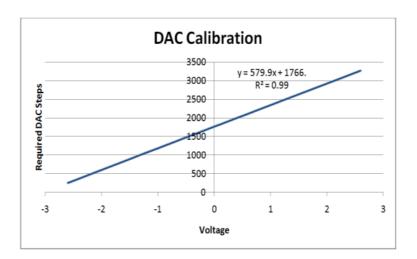

| FIGURE 6.4 CALIBRATION GRAPH & EQUATION                                            | 87       |

| FIGURE 6.5 UNIPOLAR TO BIPOLAR                                                     | 88       |

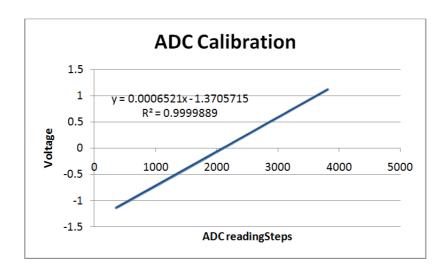

| Figure 6.6 Core schematic                                                          | 88       |

| FIGURE 6.7 CALIBRATION GRAPH & EQUATION                                            | 89       |

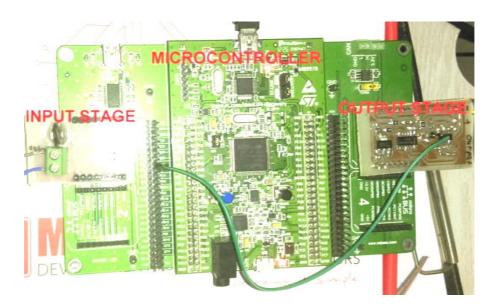

| Figure 6.8 FLC Platform                                                            | 89       |

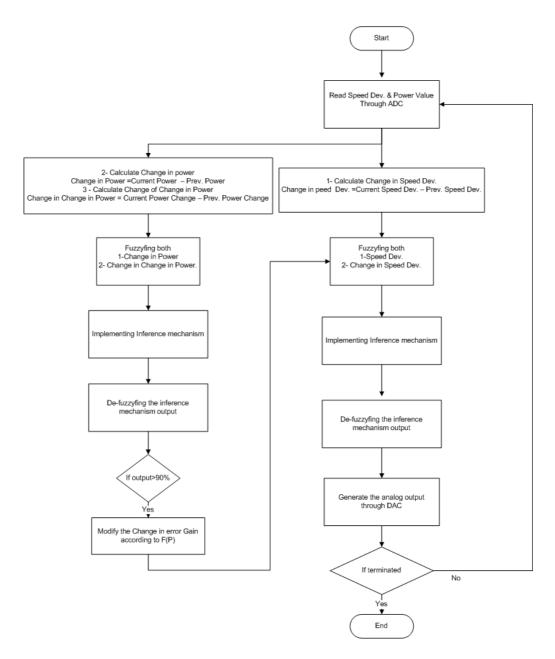

| Figure 6.9 Microcontroller Program Flow Chart                                      | 91       |

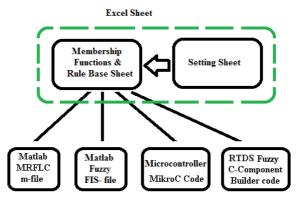

| FIGURE 6.10 MAIN FCDHT TOOL STRUCTURE                                              | 94       |

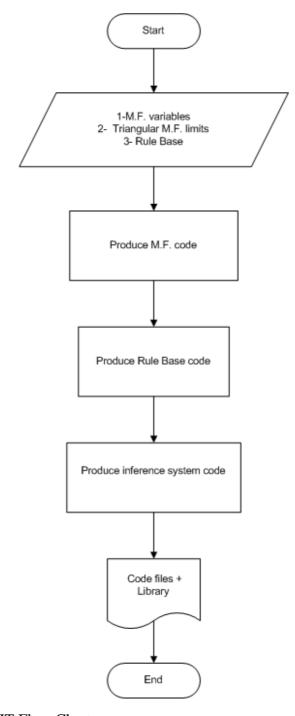

| Figure 6.11 FCDHT Flow Chart                                                       | 96       |

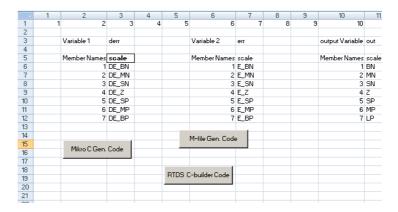

| Figure 6.12 Setting Sheet                                                          | 97       |

| FIGURE 6.13 MEMBERSHIP FUNCTIONS AND RULE BASE SHEET                               | 97       |

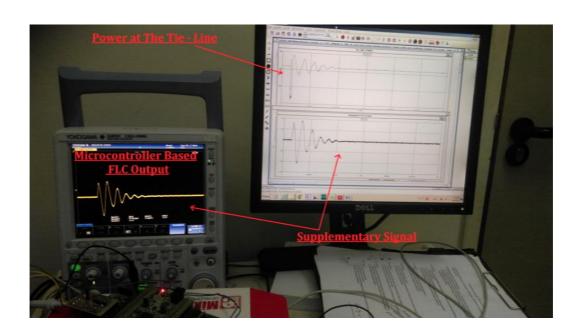

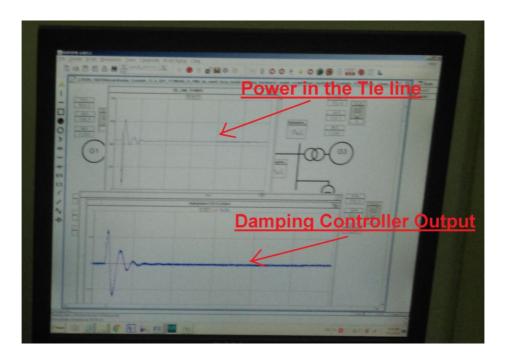

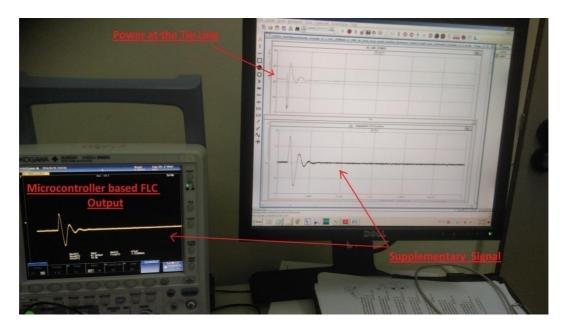

| FIGURE 6.14 EXPERIMENTAL SETUP                                                     | 98       |

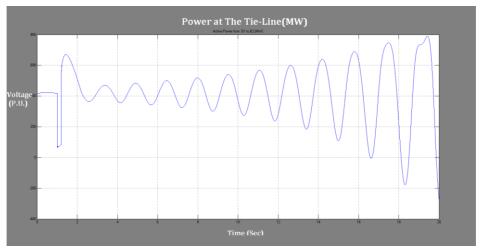

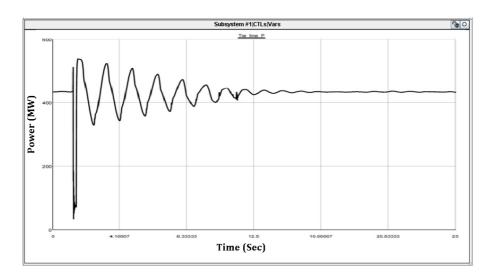

| FIGURE 6.15 POWER AT THE TIE-LINE WITH 100MVAR                                     | 99       |

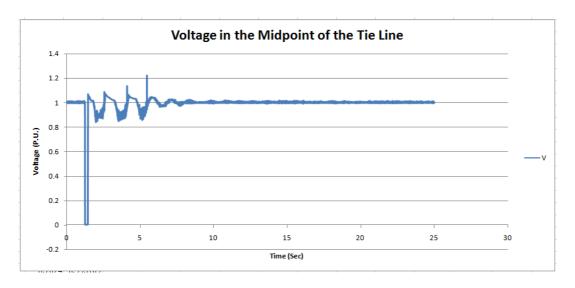

| FIGURE 6.16 VOLTAGE AT THE MIDPOINT OF THE TIE-LINE (100MVAR)                      | 99       |

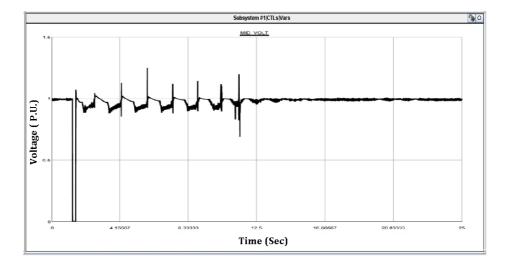

| FIGURE 6.17 POWER AT THE TIE-LINE WITH 200MVAR                                     | 100      |

| FIGURE 6.18 POWER AT THE TIE-LINE & THE SUPPLEMENTARY SIGNAL                       | 100      |

| FIGURE 6.19 VOLTAGE AT THE MIDPOINT OF THE TIE-LINE (200MVAR)                      | 101      |

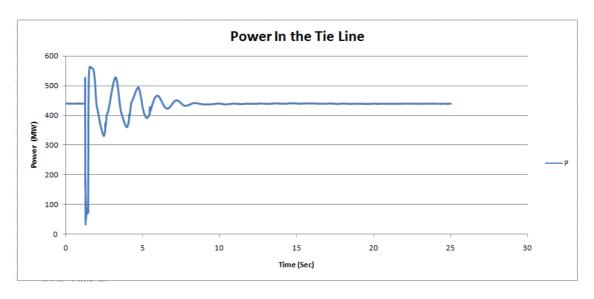

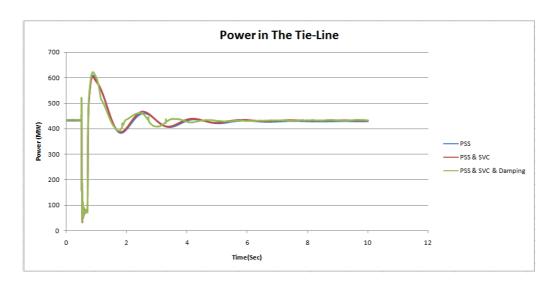

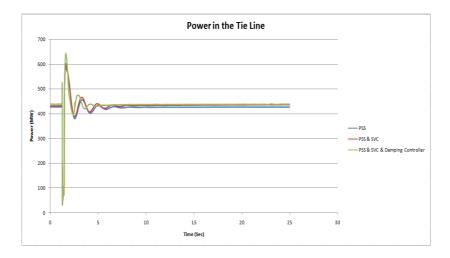

| FIGURE 6.20 COMPARING THE POWER AT TIE-LINE WITH PRESENCE OF ALL PSS, ALL PSS & SV | C, AND   |

| ALL PSS & SVC & DAMPING CONTROLLER(100MVAR SVC)                                    | 102      |

| FIGURE 6.21 POWER AT THE TIE-LINE & THE SUPPLEMENTARY SIGNAL                       | 102      |

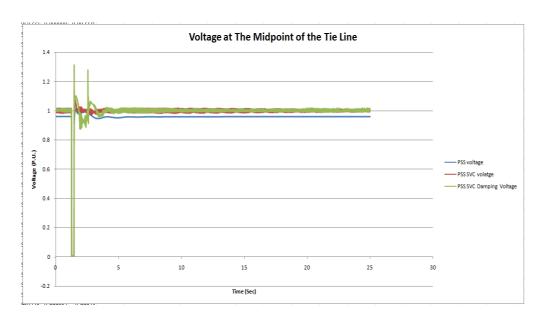

| FIGURE 6.22 COMPARING THE VOLTAGE AT THE MIDPOINT OF THE TIE-LINE WITH PRESENCE OF | ALL PSS, |

| ALL PSS & SVC, AND ALL PSS & SVC & DAMPING CONTROLLER(100MVAR SVC)                 | 103      |

| FIGURE 6.23 COMPARING THE POWER AT TIE-LINE WITH PRESENCE OF ALL PSS, ALL PSS & SV | C, AND   |

| ALL PSS & SVC & DAMPING CONTROLLER (200MVAR SVC)                                   | 103      |

| FIGURE 6.24 POWER AT THE-TIE LINE & THE SUPPLEMENTARY SIGNAL                    | 104           |

|---------------------------------------------------------------------------------|---------------|

| FIGURE 6.25 COMPARING THE VOLTAGE AT THE MIDPOINT OF THE TIE-LINE WITH PRESENCE | E OF PSS, PSS |

| & SVC, AND PSS & SVC & DAMPING CONTROLLER ( 100MVAR SVC)                        | 104           |

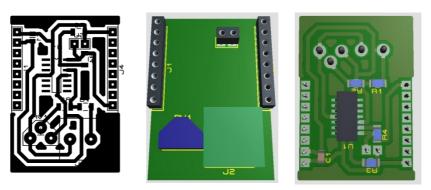

| Figure8.1                                                                       | 116           |

| Figure 8.2 PCB                                                                  | 116           |

| FIGURE 8.3 3D FRONT SIDE                                                        | 116           |

| Figure 8.4 3D Back Side                                                         | 116           |

| Figure 8.5 PCB                                                                  | 117           |

| Figure 8.6 3D Front Side                                                        | 117           |

| Figure 8.7 3D Back Side                                                         | 117           |

# **List of Abbreviation**

AC Alternative Current

ADC Analog To Digital Converter

ANFIS Adaptive Neuro-Fuzzy Inference System

AVR Automatic Voltage Regulator

CT Current Transformer

DAC Digital To Analog Converter

DFT Discrete Fourier Transform

FACTS Flexible Ac Transmission System

FC Fixed Capacitor

FCDHT Fuzzy Controller Design Helper Tool

FLC Fuzzy Logic Controller

GCC Gulf Cooperation Council

GPS Global Position System

HVDC High Voltage Direct Current

LFO Low Frequency Oscillation

MRFLC Model Reference Fuzzy Learning Controller

MVAr Mega Var

MW Mega Watt

PCB Printed Circuit Board

PI Proportional Integral

PID Proportional Integral Derivative

PMU Phasor Measurement Unit

PSS Power System Stabilizer

RTDS Real Time Digital Simulator

STATCOM Static Synchronous Compensator

SVC Static Var Compensator

TCR Thyristor Controlled Reactors

TCSC Thyristor Controlled Series Capacitor

TSC Thyristor Switch Capacitor

TSR Thyristor Switch Reactor

TSSC Thyristor Switched Series Capacitors

UPFC Unified Power Flow Controllers

VT Voltage Transformer

WAMS Wide Area Monitoring System

# Acknowledgements

First of all, I would like to express my sincere gratitude to almighty Allah and then to Dr. Khaled Ellithy and Dr. Uvais Qidwai for their constant support, expert guidance and constructive supervision.

I would also like to extend my appreciation to Eng. Abdulaziz Al Mahmoud from KAHRAMAA, and Eng. Ahmed Anad from Gdansk University of Technology for their help and support. I also thank all of those who helped me in accomplishing this work.

Finally, I must express my profound gratitude to my parents, my sisters, my wife, and my lovely son for their patience and continuous encouragement throughout the master study.

# **Chapter 1. Introduction**

#### 1.1. Power System Stability

The stability of a power system could be defined as the ability of a power system to return to the state of operational equilibrium after facing a disturbance so that the whole power system remains synchronized [1], [2]. In other words, the ability of the power system to generate opposing forces that are equal or more than the disturbance forces in order to keep the equilibrium state.

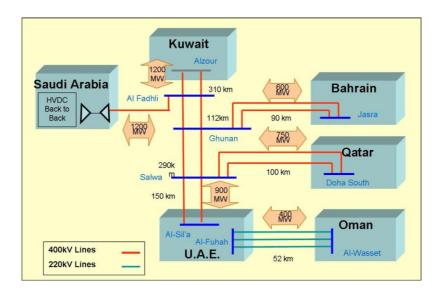

Nowadays, power systems are huge dynamic systems which are operated as interconnected systems and most of them are no longer islanded. Gulf Cooperation Council (GCC)power grid is an example of an interconnected power system as it consists of six different power systems as shown in Figure 1.1.

It is worth noting that, there are advantages and disadvantages of interconnected power systems. For instance, as advantages, it increases the system reliability as it has a better ability to support a sudden load change or generation lose. Also, an interconnected system would have higher inertia, which means that disturbances have a reduced effect. It also reduces the need of future power system expansion, as they share the spinning reserve, which lowers the spinning reserved requirement in each area / country.

On the other hand, the interconnected power systems have some disadvantages such as, the long tie-lines between adjacent power systems (ex. Qatar and Kingdom Saudi Arabia) are quite weak if it is compared with the connections within each member's power system, and this issue (weak tie-line) may lead to have low frequency oscillation (LFO).

Figure 1.1GCC interconnection Distances & Capacities [3]

Power system stability can be classified into the following categories:

- Voltage stability: which is the ability of the power system, after facing a disturbance, to keep steady voltage at all buses within the allowable limits [2].

- 2. Frequency stability: which is the ability of a power system to keep the steady frequency within the allowable limits following a cruel disturbance [2].

- Rotor Angle Stability: which is the ability of synchronous generators in a power system, after facing a disturbance, to remain in synchronism

[2].

The rotor angle stability has a major role in "power system stabilization via excitation control".

#### 1.2. Low Frequency Oscillations (LFO)

One of the main causes of having Low Frequency Oscillation (LFO)is the high gain poorly tuned generation's excitation system [2]. This issue would add a negative damping torque to the generation units, which will cause the generators to have rotor angle oscillations. LFO has a range of frequencies from 0.1 Hz to 3.0 Hz which could be considered as a small-signal stability problem. Another cause of LFO is heavy power transfer across weak tie-lines.

As mentioned above, LFO belongs to small signal stability problem which is usually a result of small disturbances, such as load changing. These disturbances would cause gradual increases or decreases in the rotor angle, and this is due to either not having enough synchronizing torque, or insufficient damping torque [4]. The inadequate damping torque could cause:

- 1- Local mode &Interplant oscillations (0.7 Hz to 2Hz) which are associated with one generating unit or within the generation plants [4].

- 2- Inter-area oscillations (0.1Hzto0.8Hz) between two areas (Group of power plants) space [4].

#### 1.3. Inter-area Oscillations

Normally, one of the main problems that could rise in heavily stressed widely spread system is the enhancement of the damping of LFO. That occurs because of inadequate damping torque in some generation units.

Traditional, Power System Stabilizer(PSS) has been used in damping the electromechanical oscillations and inter-area oscillations [5], through providing a supplementary signal to the generation excitation system.

Recently, Flexible AC Transmission System (FACTS) devices has turned into a common practice in utilities (ex. Static VAr Compensator (SVC) has been installed in KSA) for the sake of both limiting the modification in the current power systems and fully utilizing the existing transmission capacities. For instance, FACTS devices can be used instead of adding new long transmission lines (Over Head Lines) which, in some cases, could not be an economical solution, in addition to their other environmental & health impacts.

Unified Power Flow Controllers (UPFC), Thyristor Switched Series Capacitors (TSSC), and Static VAr Compensator (SVC) are examples of FACTS devices. In addition to their main advantage of having faster voltage and power flow control, adding an appropriate supplementary or auxiliary control signal to the FACTS devices can help in damping the inter-area oscillations.

#### 1.4. Flexible AC Transmission System Devices (FACTS)

FACTS devices can be divided into series devices, shunt devices, and series shunt devices. The main feature of FACTS devices is the high speed action in controlling either active power, reactive power or both, which is achieved by using power electronics, therefore, they may used to improve the power grids transient stability[6]. Static VAr Compensator (SVC)and Static Synchronous Compensator (STATCOM) are shunt devices, and their primary application is to keep the bus bar voltage at the nominal value, through their voltage regulator

controller (main controller). This controller provides synchronizing torque, whereas their damping torque contribution is small [7]. Regarding the Series Devices, such as Thyristor Controlled Series Capacitor (TCSC) devices, they are mainly used to provide power flow control over the transmission lines. By tuning the main controller parameters, their damping contribution can be slightly improved [8].

Based on above discussion, having a secondary controller (damping controller), which is necessary for generating an additional damping signal, is required for the sake of increasing the FACTS Devices damping torque.

Conventionally, supplementary or auxiliary control signal is taken or generated from the conventional damping controller that is similar to PSS in term of design. That damping controller is, usually, designed in frequency domain which limits its own performance into certain operation value/s. Using Fuzzy logic controller instead may help in extending that range to be wider, as it does not needs an accurate mathematical model to establish a good control.

Usually, the damping controller input is taken from the generation units such as speed deviation, power deviation, etc. In this thesis, speed deviation will be taken as an input. Having such input from generation would limit our self to generation units' location, which may not be adequate input for many cases. Using Phasor Measurement Unit (PMU) instead would extend our capability to have the input from any bus or substation which would add a new feature which is the mobility.

# 1.5. Static VAr Compensator

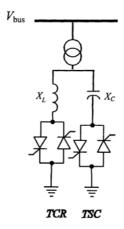

The Static VAr Compensator (SVC) is considered as shunt FACTS device as it is connected in parallel with the grid substation. The main target of SVC is to regulate the voltage at its terminals by injecting or absorbing reactive power from the power system. Based on that SVC injects reactive power when the voltage is low, and absorbs reactive power when the voltage is high. Generally, SVC consists of Thyristor controlled capacitor & inductor banks, and controlling system. These banks are connected to the power grid through step-up transformer, as shown in Figure 1.2 below.

Figure 1.2 The Basic Diagram Of The SVC

The injection or absorbing of reactive power is performed by switching capacitor banks & inductor banks on-off through Thyristor switches. The SVCs are designed in different ways/ combinations, such as Fixed Capacitors (FC) with Thyristor Controlled Reactors (TCR) and Thyristor Switched Capacitor (TSC) with TCR. TCR is controlled through courteous phase controller (firing angle) while for Thyristor Switch Reactor (TSR) is controlled through switching on-off the reactor banks (allocator is used for that) [9].

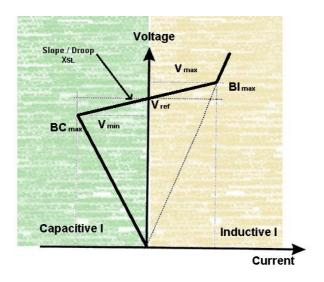

Figure 1.3 V-I Characteristic Of SVC

The SVC has a main feature which is the voltage regulation characteristic that is accomplished by controlling the current susceptance and subsequently the reactive power in the grid. The regulated voltage is following a slope (droop)

characteristic. The value of the slope is decided based on the desired voltage regulation [10]. Figure 1.3 shows dynamic voltage - current characteristics of the SVC.

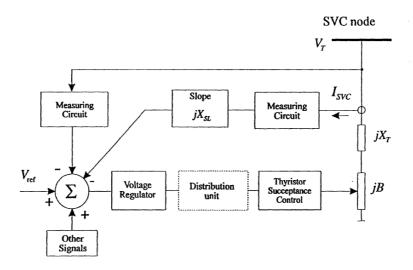

Figure 1.4 SVC Control System [11]

The voltage control system shown in Figure 1.4 consists mainly of the following modules:

Measuring Module: The module, in Figure 1.5, measuresthevoltages and currents at the Bus where the SVC is connected as well as the current flow through the SVC [11].

Figure 1.5 Measurement module [11]

Voltage Regulator Module: It uses the difference between the reference voltage and SVC terminal (error) as an input to the controller, PI regulator/ controller, in order to generate SVC susceptance reference value [11] as shown in Figure 1.6.

Figure 1.6 Voltage regulator model [10]

• Distribution Module or Allocator: It converts the voltage regulator output (susceptance reference) into the number of reactor (TSR) / capacitor (TSC)

banks that should be switched on, in addition to compute the required firing angle for TCR [11].

Figure 1.7 Thyristor Susceptance Control [10]

• Thyristor Susceptance Control Model: This block, in Figure 1.7, represent the delay associated with the firing of the Thyristor, through T<sub>d</sub> (gating transport delay) and T<sub>b</sub> (Thyristor firing sequence) [10].

#### 1.6. Pharos Measurement Unit (PMU)

Nowadays, PMUs are considered as one of the most important instrument in Wide Area Monitoring Systems (WAMS), as it is responsible for monitoring the power system. PMUs are mainly used to monitor precisely the voltage and the current phases of power systems based on GPS time-stamped reference, which is also called synchrophasors, because it helps in time aligning and synchronizing the different location measurements. Based on that power system conditions snapshot can be generated [12]. The power system snapshot plays a key role in

overcoming the voltage instability in the power systems which may lead to blackout situation. As the Instability is mainly caused by mismatching between the load dynamics, transmission lines, and generation that are needed to be monitored [13]. Figure 1.8 shows physical WAMS & PMU available in Qatar University, and Figure 1.9 shows the blocks diagram of the PMU.

Figure 1.8 WAMS & PMU in QU

Figure 1.9 PMU Blocks Diagram [14]

PMU starts with measuring the voltage and current waveforms through regular Current Transformer (CT) and Voltage Transformer (VT). After that, those waveforms signals are filtered and sampled using Analog Digital Converter (ADC). The fundamental frequency, voltage phasor and current phasor are then calculated using phasor microprocessor that use Discrete Fourier Transform (DFT). Finally, results are time-stamped using GPS and sent through communication media[14].

#### 1.7. Problem Statement

In power systems, the existence of LFO opposes the power systems objectives of having maximum power transfer and stable system. Conventionally, the solution was the generator's damper. As a result of increasing the loads, the power systems reach close to the stability operation

limits, causing a weakness in the synchronizing torque between generation units in the power system. This issue was considered as a main source of system instability. The Automatic Voltage Regulators (AVR) has then been used to help in improving the steady-state stability power systems.

The introduction of interconnected power systems with massive power transfer on long transmission lines, cause low frequency oscillations that raise a need of additional supplementary controller added to the generators' AVRs. That supplementary controller is known as the power system stabilizers. Having conventional PSS may not be sufficient in damping the inter-area oscillation which leads to use the FACTS devices with damping controller. Conventional damping controllers, such as PI, PID& lead-lag, are designed to be operated around a certain operation point, with input signals from the generation. This issue could be overcome by using damping controller based on Fuzzy logic technique combined with the PMU which will be considered as our contribution in the thesis.

#### 1.8. Objectives of the Work

The objectives of this thesis are

- To design a fuzzy logic based damping controller for SVC that will stabilize the system even without the presence of any conventional PSS at the testing system.

- Expand the Fuzzy Logic damping controller operation points by introducing online adaptive mechanism.

- Explore the possibility of using PMU as a source signals for the damping controller instead of the conventional signals source.

- Establish a Fuzzy Controller Design Helper Tool (FCDHT), for introducing a Fuzzy controller model in the Real Time Digital Simulator (RTDS)& generating microcontroller programming code as well as other important functions.

- Implement the designed Fuzzy damping controller through microcontroller and conducting Hardware In the Loop test through RTDS.

#### 1.9. Thesis Structure

#### Chapter 1:

In chapter 1, the introduction of power system stability, low frequency oscillations, inter-area oscillation, FACTS Devices, SVC, Problem statement and the objective of the work are presented.

#### Chapter 2:

In chapter 2, the conducted literature review is presented.

#### Chapter 3:

In chapter 3, the system modeling where the models of generation unit, excitation system, power system stabilizer and SVC are covered, as well as a description of the testing system (two area and four machine).

#### Chapter 4:

In chapter 4, an introduction of fuzzy logic controller as well as the design of Fuzzy Logic based SVC damping controller is presented, in

addition to the introduced adaptation mechanism.

## Chapter 5:

In chapter 5, the simulation results of MATLAB/SIMULINK as well as RTDS are presented in addition to the results of proposed adaption mechanism.

#### Chapter 6:

In chapter 6, Fuzzy Logic Controller platform preparation, Fuzzy Controller Design Helper Tool (FCDHT), and the implementation results are presented.

## Chapter 7:

In chapter 7, the conclusion and future works are presented.

# **Chapter 2.** Literature Review

Inter-area oscillation is a critical issue with interconnected power systems that may decrease the transfer capability of tie-lines between interconnected areas and deteriorate the power stability as well [15, 16]. As the electrical demand grows up, the power systems tend to operate near to their stability limits that made them more vulnerable to inter area oscillation [17]. To deal with this issue, PSS along with excitation system [18] is considered as a simple and low cost choice for enhancing the oscillation damping.

# 2.1. FACTS Devices In Damping Inter-Area Oscillation

A Variety of FACTS devices based inter-area damping controllers have been proposed and designed using Various methods such as in [19] where the Unified Power Flow Controller is based on Lyapunov-based adaptive neural network. While in [20], the Unified Power Flow Controller (UPFC) based on adaptive input-output feedback linearization control, Static VAr compensators SVCs in [21] has been used along with WAMS. High Voltage DC (HVDC) link along with model predictive controller has been proposed in [22], whereas, in [23] active-power modulation of multi-terminal has been used. However, most of the methods mentioned above are also relying on linearizing system around an operating point, that may limiting their efficiency [24].

# 2.2. Local and WAMS in Damping Controllers

With local measured signals, the damping will be mostly effective with locally observable oscillations because its observation area is limited [19]. The conventional PSSs efficiency using local signal for damping the inter-area oscillation is somehow ambiguous [25,26]. To tackle this issue, in [27] the multiband PSS has been used, while in [28]non linear PSS has been applied, and the coordinated PSS used in [29]. On the other hand, WAMS with PMUs is capable to monitor and measure the power system data such as voltage, current, angle, and frequency which give the ability to monitor wider area [30]. This method enables the remote signals to be fed to the controller to enhance the system dynamic performance more than the local measured signals [31].

Table 2.1Summary of 2.1 and 2.2

| Ref. | FACT Device                   | Controller                        | Input Signal |

|------|-------------------------------|-----------------------------------|--------------|

| 5    | Unified Power Flow Controller | Lyapunov-based adaptive neural    | Local        |

|      | (UPFC)                        | network                           |              |

| 6    | UPFC                          | adaptive input-output feedback    | WAMS         |

|      |                               | linearization                     |              |

| 7    | Static VAr compensators (SVC) | lead-lag                          | WAMS         |

| 8    | HVDC                          | model predictive                  | Local        |

| 9    | HVDC                          | Active-power modulation of multi- | WAMS         |

|      |                               | terminals                         |              |

| 11   | SVC                           | Conventional PSS                  | WAMS&        |

|      |                               |                                   | LOCAL        |

| 13   | N/A                           | multi-band PSS                    | WAMS         |

| 14   | N/A                           | non linear PSS                    | LOCAL        |

| 15   | N/A                           | Coordinated PSS                   | LOCAL        |

| 16   | Static Synchronous            | FUZZY CONTROLLER                  | WAMS         |

|      | Series Compensator (SSSC)     |                                   |              |

| 17   | N/A                           | PSS                               | WAMS         |

# 2.3. WAMS & PMUs Based Damping Controllers

Many classical and advanced controllers' design techniques utilizing WAMS have been proposed. For instance, as classical methods, modal analysis has been implemented in Norwegian transmission network in[32],and also modal analysis has been used along with time delay issue in [33],and the same thing has been applied in [34] where HVDC damping controller is designed considering 200 ms as a delay in China-southern power grid. Regarding advanced controller designing techniques, in [35] the authors has investigated multi-objective robust HVDC supplementary controller. Whereas, in [36]  $H_{\infty}$  controller has been used. Classification and regression-tree based adaptive damping control is proposed in [37] and Multivariable self-tuning feedback linearization controller is presented in [38]. Probabilistic collocation method is applied in [39], while non-linear excitation controller using inverse filtering is proposed in [40]. Networked Predictive Control Approach considering the delay in communication in [41].

Table 2.2 Summary of 2.3

| Ref.      | Technique                                | FACT / Exciter   | Remark                            |

|-----------|------------------------------------------|------------------|-----------------------------------|

| 18        | Classical (Modal Analysis)               | SVC              | In Norwegian transmission network |

| 19        | Classical (Modal Analysis)               | FACTS devices    | Time delay considered             |

| 20        | Classical (Modal Analysis)               | HVDC             | 200 ms as a delay                 |

| 21        | Advanced (Multi-Objective)               | HVDC             |                                   |

| 22        | Advanced ( $oldsymbol{H}_{\infty}$ )     | Multiple (FACTS) | Time delay considered             |

| 23        | Advanced (Classification and regression- | TCSC, SVC &ESD   | •                                 |

|           | tree based)                              |                  |                                   |

| 25        | Advanced (Probabilistic Collocation      | VSC-HVDC         | Time delay considered             |

|           | Method)                                  |                  | •                                 |

| 26        | Advanced (inverse filtering technique)   | Exciter          |                                   |

| 27        | Advanced (Networked Predictive Control   | Exciter          |                                   |

| <i>21</i> | Approach)                                | Excuei           |                                   |

#### 2.4. Robust Controller

The main objectives of designing methods are to realize a robust controllers covering wide range of operating conditions, as well as achieving some of the controller specifications.

In [37, 38,39] the controllers design is adaptive for various operating points. In [37] the robust controllers are designed off-line in line with the real-time operating point. While in [38] and [39]the controller parameters are automatically updated using real time model prediction and estimation.

#### 2.5. Classical Fuzzy Damping Controller

In [42] PID controller has been used as a main damping controller while the fuzzy controller has been used for Thyristor susceptance control. In [43] Fuzzy controller has been combined with the PI controller. The fuzzy controller has been placed in series with the integral part of the PI controller for substances control. In [44] the proposed SVC controller consists of two parts which are the traditional PI–controller as well as the supervisory fuzzy logic controller. The output of the fuzzy controller is the supplementary substances signal that will be combined with PI output.

#### 2.6. Adaptive Fuzzy Damping Controller

In[45] adaptive fuzzy controller has been used that consists of two linear damping controllers for the two extreme operating conditions in addition to a fuzzy logic adaptation mechanism. Both linear controllers' outputs are combined through weighted summation, and those weights are generated by the fuzzy

controller.. In [46] the Strategy of Oscillation Energy Descent method has been used to make the adaptive fuzzy controller. The proposed controller consists of two fuzzy controllers. One of them is the main damping controller while the other one is used for adjusting main controller's gain factors. The output of the controller is the additional amount of substances required to be either generated or absorbed by the SVC. In [47] adaptive neuro-fuzzy inference system has been used for adjusting the PI gains, main damping controller, according to the system loading conditions. In [48] Hybrid Damping controller has been introduced. It consists of PD Fuzzy controller as well as PI controller tuned by Genetic Algorithm.

| Ref. | Type of controller                                | Input                                        | Input type | Fuzzy controller enrollment                                                                                                                                                             |

|------|---------------------------------------------------|----------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28   | Classical Fuzzy<br>+PID                           | Delta Speed                                  | Local      | PID has been used as damping controller while Fuzzy controller is used to identify the amount of substances needed to be generated / absorbed by SVC.                                   |

| 29   | Classical Fuzzy +<br>PI controller                | Voltage                                      | Local      | Fuzzy Controller has been placed in series with the integration part of the PI controller.                                                                                              |

| 30   | Classical Fuzzy +<br>PI controller                | Voltage                                      | Local      | Fuzzy controller has been places in parallel with main SVC PI controller, both controllers' output are combined for having better voltage compensation.                                 |

| 31   | Adaptive Fuzzy + linear damping controller        | Power                                        | Local      | Fuzzy logic controller has been used to produce the summation weighs of both linear damping controllers.                                                                                |

| 32   | Two fuzzy controller                              | Power                                        | local      | One of them has been used as a main controller and the other one is used as gain modifier for the first fuzzy logic controller.                                                         |

| 33   | Adaptive Neuro-<br>Fuzzy Inference<br>System + PI | Power & Speed deviation                      | Local      | Adaptive Neuro Fuzzy is used to modify the gains of the main SVC PI controller.                                                                                                         |

| 34   | PD Fuzzy<br>controller + PI                       | equivalent<br>machine<br>angle<br>difference | local      | PD fuzzy controller is combined with PI controller in order to generate the supplementary damping signal, The gains of both PI & PD fuzzy controller are tuned using Genetic Algorithm. |

# 2.7. Our Contribution

In this thesis, WAMS & PMUs with SVC's robust fuzzy damping controller along with adaptation mechanism is proposed. The Fuzzy controller will be used as it can cover wider range of operating points than the conventional one. The operation range of fuzzy controller will be extended using an adaptation mechanism. WAMS & PMUs will be used as source for the controller in order to widening monitoring range as well as extending the operation points range. The system will be implemented and tested through the RTDS systems as Hardware in the Loop.

# **Chapter 3. Power System Modeling**

In this chapter, the models of the generators, AVR and PSS used in the testing system (two area, four machine system) are described in fairly details.

### 3.1. Generator Model

For stability studies, several models can be used in modeling synchronous generators, some of them include damper windings and some are not. In the sixth order model, the generator has four windings, two are in the q-axis and the rest are in the d-axis. In this model, the network and stator transients are neglected which will lead to conservative results, and this issue is preferred in stability studies [49]. This model of synchronous machine is usually described by six equations as follows [50].

$$\frac{d}{dt}E_{d}^{'} = \frac{1}{T_{q0}^{'}} \left[ -E_{d}^{'} + (X_{q} - X_{q}^{'}) \left\{ I_{q} - \frac{X_{q}^{'} - X_{q}^{''}}{\left(X_{q}^{'} - X_{lk,s}\right)^{2}} (\psi_{2q} + \left(X_{q}^{'} - X_{lk,s}\right) I_{q} + E_{d}^{'} \right\} \right]$$

3.1

$$\frac{d}{dt}E_{q}^{'} = \frac{1}{T_{d0}^{'}} \left[ -E_{q}^{'} + (X_{d} - X_{d}^{'}) \left\{ I_{d} - \frac{X_{d}^{'} - X_{d}^{''}}{\left(X_{d}^{'} - X_{lk,s}\right)^{2}} (\psi_{1d} + \left(X_{d}^{'} - X_{l}\right) I_{d} + E_{q}^{'} \right\} \right] \quad 3.2$$

$$\frac{d}{dt}\psi_{1d} = \frac{1}{T_{d0}^{"}} \left[ -\psi_{1d} + E_{q}^{'} - (X_{d}^{'} - X_{l})I_{d} \right]$$

3.3

$$\frac{d}{dt}\psi_{2q} = \frac{1}{T_{q0}^{"}} \left[ -\psi_{2q} + E_{d}^{'} - (X_{q}^{'} - X_{lk,s})I_{q} \right]$$

3.4

$$\frac{d}{dt}\omega_r = \frac{1}{2H}[P_m - P_e - D \triangle \omega_r]$$

3.5

$$\frac{d}{dt}\delta = (\omega_r - \omega_{syn}) = \Delta \omega_r \tag{3.6}$$

### Where:

$X_d$ : Synchronous Reactances in d-axes

$X_q$ : Synchronous Reactances q-axes

$X'_d$ : Transient Reactances of d- axes

$X'_q$ : Transient Reactances of q-axes

$X_d''$ : Sub-Transient Reactances of d-axes

$X_q''$ : Sub-Transient Reactances of q-axes

$X_1$ : Leakage Inductance

$T'_{d0}$ : Transient Time Constant of d-axes

$T'_{a0}$ : Transient Time Constant of q-axes

$T_{d0}^{"}$ : Sub-Transient Time Constant of d -axes

$T''_{a0}$ : Sub-Transient Time Constant of q-axes

H : Inertia Constant, stored energy at rated speed,

$I_d$ : Armature Current of d-axis

$I_a$ : Armature Current of q-axis

$\psi_{1d}$  : Flux Linkage Damper Winding of d-axis

$\psi_{2q}$ : Flux Linkage Damper Winding of q-axis

$P_{\rho}$ : Electrical Power

$P_m$ : Mechanical Torque

$\omega_r$ : Generator Rotor Speed

$\omega_{syn}$ : Rated Generator Rotor Speed (2 $\pi$ f)

$E'_d$ : Transient Voltage in d-axes  $E'_q$ : Transient Voltage in q-axes

δ : Rotor Angle

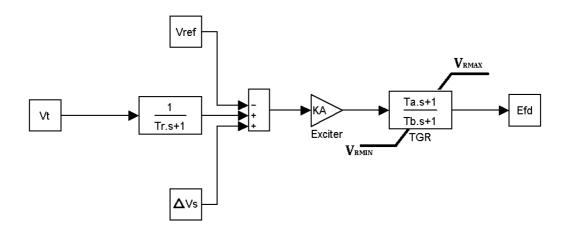

### 3.2. Excitation System Models

The excitation system's main objective is to regulate the generation terminal voltage through controlling the field current. As the time constant of field current is usually high, in term of seconds, fast control is required. Therefore,

exciter should have a very high voltage output. The used exciter, as shown in Figure 3.1, is Fast Exciter (Static Exciter) [51].

Figure 3.1 Exciter Model Static Exciter [51]

### Where:

K<sub>A</sub> : Exciter Gain

T<sub>r</sub> : Transducer Time constant

T<sub>a</sub>& T<sub>b</sub> : Transient Gain Reduction lead-lag time constant

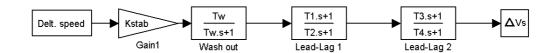

### 3.3. Power System Stabilizer

The main aim of the PSS is to enhance the angular stability limits and to damp out the oscillation in synchronous machines' rotors through providing a supplemental signal to the generator's excitation system. The PSS supplementary control signal (Vs) is very useful during huge power transfers, as it increases the tie-line thermal limit by damping the oscillation [52, 53]. However, the PSS negative damping effects on the machine's rotor may lead to instability, as the conventional PSS is usually tuned around certain operating point where their

efficiency is within small range around it [53]. During large disturbances, a Power System stabilizer may cause the generators to lose synchronism as it is trying to control the excitation field [53]. Figure 3.2 shows the PSS Model used.

It is worth noting that washout block is used to eliminate the DC component from the signal &Lead –Lag blocks are used for phase compensation.

Figure 3.2 PSS Model

### where:

$K_{stab}$ : Stabilizer Gain

$\begin{array}{lll} T_w & : & Washout \ Time \ Constant \\ T_1 \ \& & : & Lead \ Lag \ 1 \ Time \ Constants \end{array}$

$T_2$

T<sub>3</sub> & : Lead Lag Time Constants

$T_4$

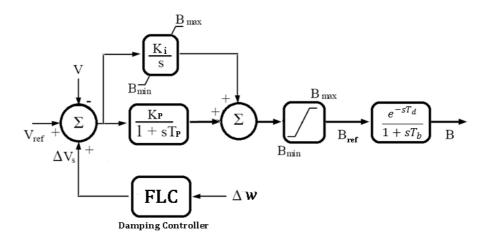

### 3.4. Static VAr Compensators

The main aim of SVC is to regulate the voltage at its terminals by injecting or absorbing reactive power. Figure 3.3 below shows the basic block diagram of SVC, which mainly consists of a PI controller that represents the voltage regulator part. The voltage regulator input is the difference between the reference voltage and the bus voltage (error) in addition to the damping controller signal, while the

controller output is the susceptance value required from the SVC to generate or absorb.

Figure 3.3 SVC Basic Block Diagram of SVC Model [54]

Where:

$$\frac{K_p}{1 + sT_p}$$

The proportional part of the voltage regulator

$$\frac{K_i}{\frac{S}{S}}$$

The Integrator part of the voltage regulator

$$\frac{e^{-sT_d}}{1 + sT_b}$$

Thyristor succeptance control

The typical values for the controller are shown in the Table3.1below.

Table 3.1 Typical Values of SVC controller [51]

| Module            | Parameter  | Definition                      | Typical values                        |

|-------------------|------------|---------------------------------|---------------------------------------|

| Measuring         | $T_{m}$    | Measuring Time constant         | 0.001s - 0.005s                       |

| Thyristor Control | $T_{d}$    | Gating transport delay          | 0.001s                                |

|                   | $T_{b}$    | Thyristor firing sequence delay | 0.003s - 0.006s                       |

| Voltage regulator | $K_i, K_p$ | Integrator& Proportional Gain   | Vary based on how fast & well damping |

| Slope             | $X_{SL}$   | Slope, Droop                    | 0.01-0.05 p.u.                        |

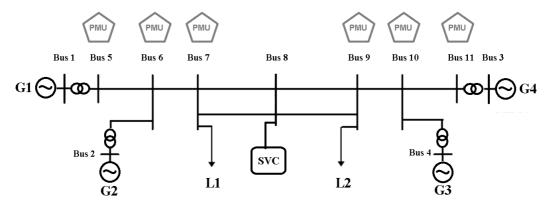

### 3.5. Testing System

Figure 3.4 Testing System [51]

Figure 3.4 shows the single line diagram of the two-area, four-machine power system (as well as the PMUs location) that is used for testing the inter-area oscillation problem [49]. Based on that, this system has become a reference for inter-area oscillation problem [49]. In this system, there are four generators, GEN1 and GEN2 are in area one, while GEN3 and GEN4 are in area two. All of

the generators are associated step up 20kV/230kV transformers. Two loads allocated at buses 7 and 9 with 967MW and 1767MW respectively. SVC is installed in the midpoint of the tie-line at Bus 8 with capacities of 100MVAr& 200MVAr. The testing system model parameters are shown in Tables3.2to 3.8 [49].

Table 3.2 Transformer Parameters [49]

| Transformers Parameters ( Based on 900MVA) |        |                          |                          |  |  |  |  |

|--------------------------------------------|--------|--------------------------|--------------------------|--|--|--|--|

| From Bus                                   | To Bus | <b>R</b> ( <b>P.U.</b> ) | <b>X</b> ( <b>P.U.</b> ) |  |  |  |  |

| 1                                          | 5      | 0.0                      | 0.15                     |  |  |  |  |

| 2                                          | 6      | 0.0                      | 0.15                     |  |  |  |  |

| 3                                          | 11     | 0.0                      | 0.15                     |  |  |  |  |

| 4                                          | 10     | 0.0                      | 0.15                     |  |  |  |  |

Table 3.3 Branches Parameters [49]

| Line Parame | Line Parameters ( Based on 100MVA) |        |                |        |       |         |  |  |  |

|-------------|------------------------------------|--------|----------------|--------|-------|---------|--|--|--|

| From Bus    | ID                                 | To Bus | Length(<br>km) | R(PU)  | X(PU) | B(PU)   |  |  |  |

| 5           | 1                                  | 6      | 25             | 0.0025 | 0.025 | 0.04375 |  |  |  |

| 6           | 1                                  | 7      | 10             | 0.001  | 0.01  | 0.0175  |  |  |  |

| 7           | 1                                  | 8      | 110            | 0.011  | 0.11  | 0.1925  |  |  |  |

| 7           | 2                                  | 8      | 110            | 0.011  | 0.11  | 0.1925  |  |  |  |

| 8           | 1                                  | 9      | 110            | 0.011  | 0.11  | 0.1925  |  |  |  |

| 8           | 2                                  | 9      | 110            | 0.011  | 0.11  | 0.1925  |  |  |  |

| 9           | 1                                  | 10     | 10             | 0.001  | 0.01  | 0.0175  |  |  |  |

| 10          | 1                                  | 11     | 25             | 0.0025 | 0.025 | 0.04375 |  |  |  |

Table 3.4 Load Flow Data [49]

| Generator<br>Load | / | Voltage (PU) | Angle  | P (MW) | Q (MVAr) |

|-------------------|---|--------------|--------|--------|----------|

| G1                |   | 1.03         | 18.56  | 700    | 185      |

| G2                |   | 1.01         | 8.8    | 700    | 235      |

| G3                |   | 1.03         | -8.5   | 719    | 176      |

| G4                |   | 1.01         | -18.69 | 700    | 202      |

Table3.5Loads [49]

| Bus | $P_{\rm L}$ | $Q_{\rm L}$ | $Q_{C}$ |

|-----|-------------|-------------|---------|

| 7   | 967         | 100         | 200     |

| 9   | 1767        | 100         | 350     |

Table 3.6 Generator Parameters [49]

| Generators Pa               | arameter (Based on 90 | 00MVA, 20kV)    |

|-----------------------------|-----------------------|-----------------|

| Parameter                   | Generators 1, 2       | Generators 3, 4 |

| Xd                          | 1.8                   | 1.8             |

| X'd                         | 0.3                   | 0.3             |

| X''d                        | 0.25                  | 0.25            |

| Xq                          | 1.7                   | 1.7             |

| X'q                         | 0.55                  | 0.55            |

| X''q                        | 0.25                  | 0.25            |

| T'do                        | 8.0                   | 8.0             |

| T''do                       | 0.03                  | 0.03            |

| T'qo                        | 0.4                   | 0.4             |

| T''qo                       | 0.05                  | 0.05            |

| $A_{sat}$                   | 0.015                 | 0.015           |

| $\mathbf{B}_{\mathrm{sat}}$ | 9.6                   | 9.6             |

| Н                           | 6.5                   | 6.175           |

| $R_a$                       | 0.0025                | 0.0025          |

| Xl                          | 0.2                   | 0.2             |

| $\Psi_{\mathrm{T1}}$        | 0.9                   | 0.9             |

| $K_D$                       | 0                     | 0               |

Table 3.7 Exciter & PSS Parameters [49]

| Parameter  | Value |

|------------|-------|

| $K_A$      | 200   |

| $T_R$      | 0.01  |

| $T_a$      | 0     |

| $T_b$      | 0     |

| $K_{Stab}$ | 20    |

| $T_{W}$    | 10    |

| $T_1$      | 0.05  |

| $T_2$      | 0.02  |

| $T_3$      | 3     |

| $T_4$      | 5.4   |

Table 3.8 SVC Parameters

| Parameter            | Value     |               |

|----------------------|-----------|---------------|

| Reactive power limit | ± 100MVAr | $\pm$ 200MVAr |

| C                    | 1029.9 uf | 2059.8 uf     |

| L                    | 5.0399 mH | 2.51995 mH    |

| $T_d$                | 0.001     |               |

| $X_{SL}$             | 0.03      |               |

| $\mathbf{K}_{p}$     | 0         |               |

| $K_i$                | 300       |               |

# **Chapter 4.** Design of Fuzzy Logic Damping Controller

### 4.1. Introduction

Lofty A. Zadeh, in 1965, published "Fuzzy Sets" where the mathematical theory and logic have been represented [56]. His main idea was to let the digital computers to represent unclear ideas as what the human can do, in order to allow the computers to threat the data similar to human reasoning.

FLC effectiveness appears when the plant, needed to be controlled, is difficult to be modeled, whereas the experienced operator is available. FLC main idea is to emulate the operator qualitative way / rules of controlling the system.

FLC has several advantages over the conventional controllers such as:

- The simplicity, as it is based on the linguistic rules (human logic) based on IF-THEN structure.

- Does not need an accurate system model of the plant.

- Can deal with nonlinear systems.

- Does not need clear data and can work with approximate data.

# 4.2. Fuzzy Logic Controller (FLC)

Figure 4.1 shows the fuzzy logic control system's block diagram

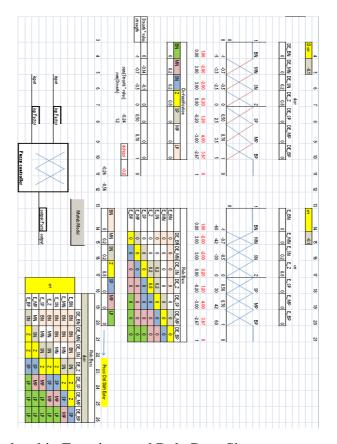

# Rule Base | Sept | 150 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100

Figure 4.1 FLC Stages

# The FLC consists of the following four main stages:

- Fuzzification stage, in which the regular / crisp inputs are converted into linguistic Variables in order to help the inference engine in executing the rule base.

- 2. Knowledge Base or Rule Base (set of multiple If-Then rules), that contains the linguistic knowledge of the expert of describing how to accomplish a good control of the plant.

- 3. Inference engine, which emulates the expert decision of how to apply the knowledge base in controlling the plant.

4. De-Fuzzification stage, where the inference engine's linguistic outputs is converted into crisp outputs.

# **4.2.1 Fuzzification Stage:**

In this stage, the controller's inputs will be transformed from its original form, crisp, into linguistic form that is closer to the human way of thinking using membership functions.

The membership functions are functions that linked the crisp Variables, in a certain region, with the percentage of belonging (0 %--> 100%) to a membership. These membership functions will have names used in our daily life (linguistic values/ labels) such as big, medium, or small.

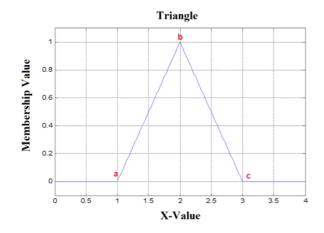

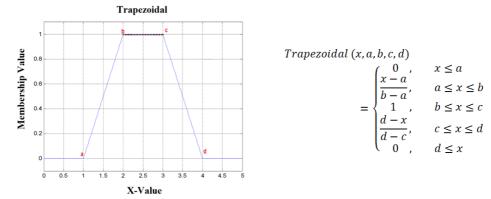

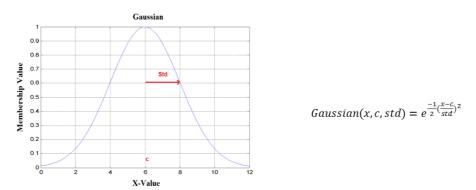

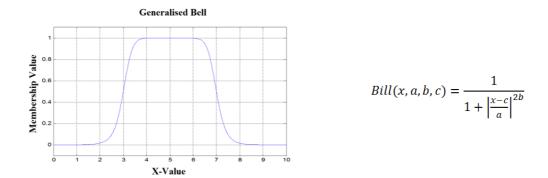

There are Various types of membership functions some of them are described below in Figures 4.2 to 4.6.[57]

$$Triangle \ (x,a,b,c) = \begin{cases} 0 &, & x \le a \\ \frac{x-a}{b-a}, & a \le x \le b \\ \frac{c-x}{c-b}, & b \le x \le c \\ 0 &, & c \le x \end{cases}$$

Figure 4.2 Triangle Membership Function

Figure 4.3 Trapezoidal Membership Function

Figure 4.4 Gaussian Membership Function

Figure 4.5 Generalized Bill Membership Function

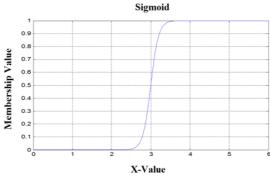

Figure 4.6 Sigmoid Membership Function

$$Sig(x, a, c) = \frac{1}{1 + e^{[-a(x-c)]}}$$

# 4.2.2 The Rule / Knowledge Base

As mentioned above the rule base contains the linguistic rules description of the expert knowledge of how to control the plant, in other words it is a Table that shows the relationship between the inputs and the outputs, in form of IF-THEN relationship. For instance,

IF <u>Error</u> is Big Positive AND <u>Change in Error</u> is Big Negative THEN

**Output** is Small Negative.

### 4.2.3 Inference Engine / Mechanism

It is the engine that determines the conclusions after applying the rule base or knowledge base. It is conducted by evaluating each rule independently, and then combines all of the rules output to determine controller linguistic output. There are two main inference systems Mamdani, and Sugeno.

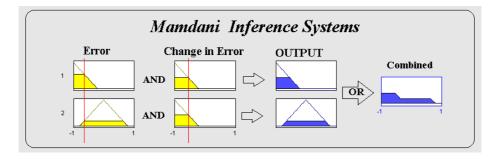

# A. Mamdani Inference Systems

Figure 4.7 Mamdani Inference System

In Figure 4.7, there are two FLC rules in the form of

```

R<sub>1</sub>: if Error is X_1 and Change in Error is Y_1 then Output is C_1

R<sub>2</sub>: if Error is X_2 and Change in Error is Y_2 then Output is C_2

```

Basically, it starts the AND operation which is the min of (Error & Change in Error) for each rule, and then the overall system output is calculated by combining those individual rule outputs, by union operation / OR operation.

# B. Sugeno Inference Systems

The Sugeno Inference system or T-S inference system introduced in 1985[58]. It has the same form of Mamdani inference system but with output as a function of the inputs. In others words, it has no output membership function, and the output is computed evaluating the function.

The following is the form:

R1: if Error is  $X_1$  and Change in Error is  $Y_1$  then Output is z = f(Error ,Change in Error)

In case, z = f (Error, Change in Error) is a polynomial of first order, and then the Sugeno fuzzy model is named as first order. Whereas, if z is a constant, then the Sugeno fuzzy model is called a zero order.

### 4.2.4 De-Fuzzification

In de-fuzzification, the linguistic output of the inference system is converted in to crisp output. There are many types for De-fuzzification methods such as Center of Gravity (COG), Mean of Maximum (MOM), Min-Max, Weighted Average Formula (Min – Max WAF), Center of Sum (COS), ...etc [59], and we will limit our self to three of the most common methods which are Center of Gravity (COG), Mean of Maximum (MOM), and Weighted Average(WAF) [59,60]

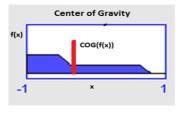

# A. Center of Gravity (COG)

In the center of gravity method, the center location of the total area of the inference engine's output is computed by using the following formulas [59]:

Figure 4.8 Center of Gravity

For continuous signal version:

$$COG(f(x)) = \frac{\int_{-\infty}^{\infty} f(x).x \ dx}{\int_{-\infty}^{\infty} f(x)dx}$$

Discrete Version:

$$COG(f(x)) = \frac{\sum_{i=0}^{n} f(x_i).x_i}{\sum_{i=0}^{n} f(x_i)}$$

Where:

f(x) is the degree of membership function

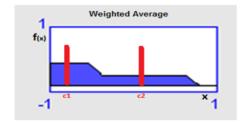

# B. Weighted Average

This is another method of de-Fuzzification which can be implemented by using the following equation [59].

$$WA = \frac{\sum_{i=1}^{n} f(c_i).c_i}{\sum_{i=1}^{n} f(c_i)}$$

Figure 4.9 Weighted Average

Where:

Ci is the center of output membership function

f(Ci) is the degree of membership function

# C. Mean of Maximum

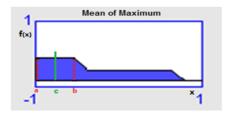

MOM is the average of the maximizing membership as shown in Figure 4.10. The average of the maximum range can be calculated as the following [59].

$$MOM = \frac{\int_a^b x \, dx}{\int_a^b dx} = \frac{a+b}{2}$$

Figure 4.10 Mean Of Maximum

# 4.3. Design of Fuzzy Logic Damping Controller for SVC

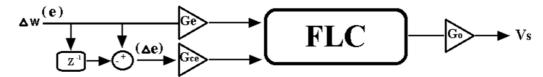

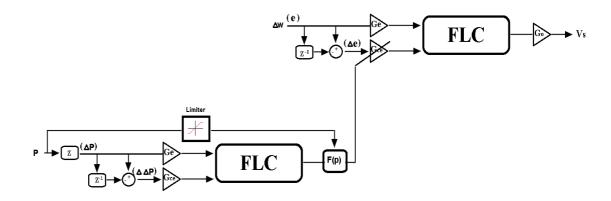

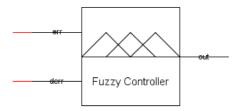

Figure 4.11 shows the basic structure of the controller

Figure 4.11 Damping Controller Structure

### **4.3.1** Choosing The Controller Inputs

As a starting point, the controller inputs are needed to be chosen such a way that they can help in figuring out the power oscillation in the systems, based on that both the change in power and generation speed deviation can be used. Changing in power may not be a proper choice because the power is not constant as it changes all over the day/ session / year. On the other hand, Speed deviation can be used as it is inversely proportional to the change in the power. Because there is relationship between the speed and the frequency which is the  $2\pi$ , and also

there is another relationship between the power and the frequency which is that the system frequency will goes down if the power goes up and vice versa.

Therefore the change in speed could be a better choice as the existing systems has either 314 RPM (50Hz) or 377PRM (60Hz). Hence, both Speed deviation and its derivative have been chosen as inputs to the FLC.

### **4.3.2** Choosing The Membership Functions Limits:

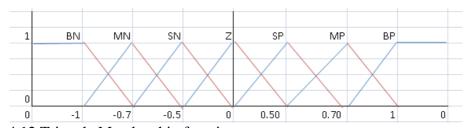

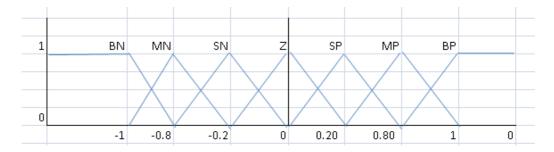

Many possibilities have been investigated in order to find out what could be considered as semi optimal and they are shown below Figure 4.12. Appendix-C show some of the membership function's tested limits.

Figure 4.12 Triangle Membership function

### **4.3.3 Fuzzification Stage**

As one of thesis targets is to implement the controller practically through the microcontroller and RTDS, therefore, a Fuzzification method that needs less computational power has to be chosen. In other words, in order to let the controller to be a real-timecontroller, it should be able to response to the input in immediately. Based onabove, triangle membership function, shown in Figure 4.12,

has been chosen. Furthermore the triangle membership function could be considered as an approximation to the Gaussian membership function.

In Fuzzification stage, seven linguistic Variables per input & output have been chosen forming a total of 21 linguistic Variables, and they are presented in Table 4.1.

Table 4.1 Linguistic Variables

| # | Variable        | Speed Dev. | Change in Speed | Output |

|---|-----------------|------------|-----------------|--------|

|   |                 |            | Dev.            |        |

| 1 | Big Negative    | E_BN       | DE_BN           | BN     |

| 2 | Medium Negative | E_MN       | DE_MN           | MN     |

| 3 | Small Negative  | E_SN       | DE_SN           | SN     |

| 4 | Zero            | E_Z        | DE_Z            | Z      |

| 5 | Small Positive, | E_SP       | DE_SP           | SP     |

| 6 | Medium Positive | E_MP       | DE_MP           | MP     |

| 7 | Big Positive    | E_BP       | DE_BP           | BP     |

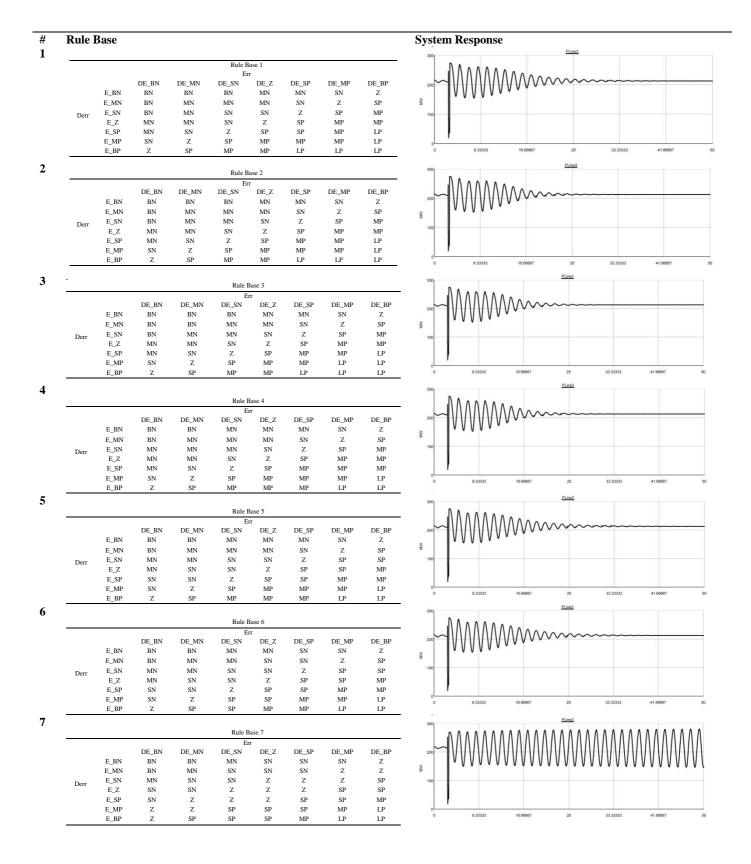

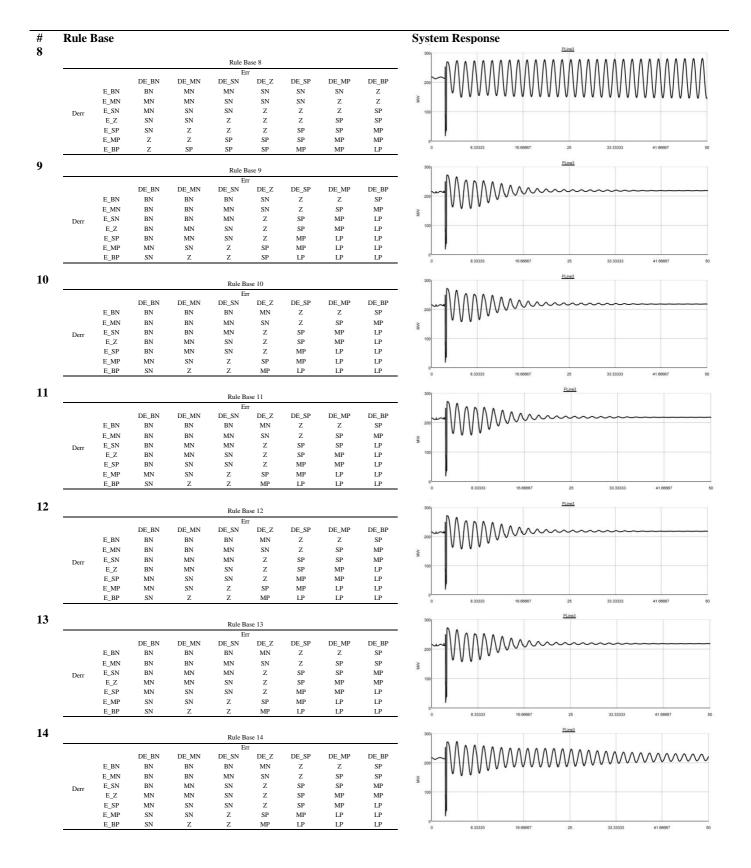

# 4.3.4 Inference Engine & Rule Base

Mamdani method has been chosen for the hardware implementation due to its simplicity. Based on the lowest settling time criteria, fifteen rule bases (7x7) have been tested prior to choosing the one shown in Table 4.2 for the damping controller. Actually, two rule bases have been chosen No.3 & No.9 (in Appendix-B) but with further investigation (combined source signal input) it is found out that Table 4.2 could be consider as the best rule base among them. Appendix-B

contains the tested 15 rule bases and the related system performance (based on single source input).

Table 4.2 Main Controller Rule Base

|     |      | derr  |       |       |      |       |       |       |  |

|-----|------|-------|-------|-------|------|-------|-------|-------|--|

|     |      | DE_BN | DE_MN | DE_SN | DE_Z | DE_SP | DE_MP | DE_BP |  |

|     | E_BN | BN    | BN    | BN    | SN   | Z     | Z     | SP    |  |

|     | E_MN | BN    | BN    | MN    | SN   | Z     | SP    | MP    |  |

|     | E_SN | BN    | BN    | MN    | Z    | SP    | MP    | LP    |  |

| Err | E_Z  | BN    | MN    | SN    | Z    | SP    | MP    | LP    |  |

|     | E_SP | BN    | MN    | SN    | Z    | MP    | LP    | LP    |  |

|     | E_MP | MN    | SN    | Z     | SP   | MP    | LP    | LP    |  |

|     | E_BP | SN    | Z     | Z     | SP   | LP    | LP    | LP    |  |

### 4.3.5 De-Fuzzification

The main purpose of the de-Fuzzification stage is to convert the linguistic Variables from the inference engine into crisp output value. Weighted average method described earlier in this chapter has been used, as it does not need huge computational power compared to the other techniques / methods. Furthermore, it does not need output triangle membership functions.

# 4.3.6 Controller Tuning (Choosing Gain's Values Ge, Gce & Go)

The controller has been designed such a way that it can be tuned by changing some gains. Those gains are Ge, Gce and Go which are Error gain (speed deviation), Change in error gain (change in speed deviation), and output gain respectively.

Based on above the tuning process has been as follows:

- 1. Finding the limits of each gain

- 2. Conducting a deep searching within the limits

## Stage 1:

In order to find the limits or the initial gains the steps below has been followed:

- 1. The Error or the speed deviation has been found by conducting many simulation scenarios plus adding 10 % on the top of the max reading as a safety margin to keep the read values away from the saturation.

- 2. The range of change in Speed deviation has been identified using trial and error to find the initial values.

- 3. By trial and error the output gain has been identified.

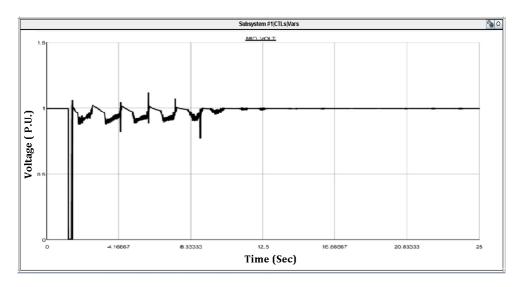

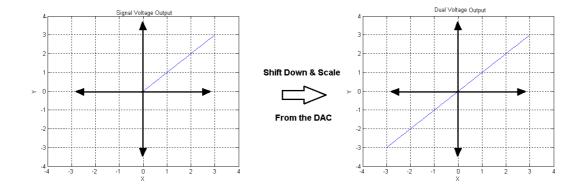

### Stage 2: