# QATAR UNIVERSITY

#### **COLLEGE OF ENGINEERING**

# TRANSFORMERLESS MICROINVERTER WITH LOW LEAKAGE CURRENT CIRCULATION AND LOW INPUT CAPACITANCE REQUIREMENT FOR PV APPLICATIONS

BY

#### Ahmad Mirdad Khan

A Thesis Submitted to the Faculty of

College of Engineering

in Partial Fulfillment

of the Requirements

for the Degree of

Master of Science in

**Electrical Engineering**

January 2017

© 2017 Ahmad Mirdad Khan. All Rights Reserved.

# **COMMITTEE PAGE**

The members of the Committee approve the thesis of  $\bf Ahmad~Mirdad~Khan$  defended on  $\bf 8/1/2017$

|                                                 | Prof.                             |

|-------------------------------------------------|-----------------------------------|

|                                                 | Lazhar Ben-Brahim                 |

|                                                 | Thesis/Dissertation Supervisor    |

|                                                 | Prof.                             |

|                                                 | Adel Gastli                       |

|                                                 | Thesis/Dissertation Co-Supervisor |

|                                                 | <br>Dr.                           |

|                                                 | Mounir Bouzguenda                 |

|                                                 | Committee Member                  |

|                                                 | Dr.                               |

|                                                 | Ahmed Massoud                     |

|                                                 | Committee Member                  |

|                                                 | Dr.                               |

|                                                 | Hasan Mehrjerdi                   |

|                                                 | Committee Member                  |

|                                                 |                                   |

| Approved:                                       |                                   |

|                                                 |                                   |

| Dr. Khalifa Al-Khalifa, Dean, College of Engine | eering                            |

|                                                 |                                   |

#### **ABSTRACT**

The inevitable depletion of limited fossil fuels combined with their harmful footprint on the environment led to a global pursuit for alternative energy sources that are clean and inexhaustible. Renewable energies such as wind, biomass and solar are the best alternative energy candidates, with the latter being more suitable for GCC countries. Besides, the energy generated from photovoltaic (PV) modules is one of the elegant examples of harnessing solar energy, as it is clean, pollutant-free and modular. Furthermore, recent advances in PV technology, especially grid-connected PV systems revealed the preeminence of using multiple small inverters called (Microinverters) over using the conventional single inverter configuration. Specifically, the break-even cost point can be reached faster and the system modularity increases with microinverters usage. Nonetheless, due to microinverter's small ratings designers prefer transformerless designs because transformer removal achieves higher efficiency and power density. However, the transformer removal results in loss of galvanic isolation that leads to dangerous leakage current circulation that affects system safety. Another issue with microinverters is that since they are installed outside their bulky DC-Link electrolytic capacitor lifetime deteriorates the system reliability because electrolytic capacitor failure rate increases as temperature increases. Moreover, the DC-Link capacitor is used to decouple the 2<sup>nd</sup> order power harmonic ripples that appear in single-phase systems. Thus, the objective of this thesis is to design an efficient transformerless microinverter that has low leakage current circulation and low input capacitance requirement with a minimum number of active switches. In other words, the objective is to increase the safety and the reliability of the system while maintaining the high efficiency. Eventually, the configuration selected is the transformerless differential buck microinverter with LCL filter and it is modeled with passive resonance damping and active resonance damping control.

#### **ACKNOWLEDGEMENT**

First, I would like to thank my loving family and fiancée for their unconditional love and support. As well as, I would like to express my gratitude to my supervisors Prof. Lazhar Ben-Brahim and Prof. Adel Gastli for their wisdom, patience, encouragement, and continuous support throughout this thesis. Their guidance and support were the most crucial assets that led me to complete this thesis successfully. Also, I would like to extend my gratitude to the Qatar University's electrical engineering department for providing me with the required technical knowledge and support whenever help was needed.

# **Table of Contents**

| ACKNOWLEDGEMENTv                                                               |

|--------------------------------------------------------------------------------|

| List of Figuresx                                                               |

| List of Tablesxiv                                                              |

| Chapter 1 : Introduction                                                       |

| 1.1. Background                                                                |

| 1.2. Thesis Objective                                                          |

| 1.3. Thesis Scope5                                                             |

| 1.4. Thesis Outline5                                                           |

| Chapter 2 : Literature Review6                                                 |

| 2.1. Leakage Current Review6                                                   |

| 2.1.1 Common Mode Voltage and Leakage Current7                                 |

| 2.1.2. Leakage Current Relation with the PWM Scheme                            |

| 2.1.3. Mitigation Methods                                                      |

| 2.1.3.1. Elimination of Leakage Current with Active Switches Modification16    |

| 2.1.3.2. Elimination of Leakage Current without Active Switches Modification28 |

| 2.2. Double Grid Frequency Power Ripples Review                                |

| 2.2.1. Double Grid Frequency Power Ripples and DC-Link Capacitor Size33        |

| 2.2.2. Input Capacitance Reduction Methods and Power Decoupling Control37      |

| 2.2.2.1. Differential Microinverter Configurations                             |

| 2.2.2.2. Differential Buck Microinverter Operation                    | 39 |

|-----------------------------------------------------------------------|----|

| 2.2.2.3. Basic Power Decoupling Technique                             | 41 |

| 2.2.3. Power Decoupling Schemes in Differential Microinverters        | 42 |

| Chapter 3 : Comparison Study                                          | 46 |

| 3.1. Conventional Configuration with Different PWM Schemes Simulation | 46 |

| 3.2. DC-Based Decoupling Network Type Simulation                      | 47 |

| 3.3. AC-Based Decoupling Network Type Simulation                      | 48 |

| 3.4. LC CM Filter Simulation                                          | 49 |

| 3.5. Comparison Study Conclusion                                      | 50 |

| 3.6. Topology Modification to Eliminate the Power Ripples             | 52 |

| Chapter 4 : Design Methodology                                        | 54 |

| Chapter 5 : Modelling and Microinverter Control                       | 56 |

| 5.1. Differential Buck with LCL Passive Resonance Damper              | 56 |

| 5.1.1. Filter Design                                                  | 56 |

| 5.1.2. Controllers Design                                             | 60 |

| 5.1.2.1. DM controller                                                | 60 |

| 5.1.2.2. CM controller                                                | 64 |

| 5.1.3. Overall Control with Passive Resonance Damper                  | 68 |

| 5.2. Differential Buck with LCL with Active Resonance Damper          | 70 |

| 5.2.1 Small Signal Analysis                                           | 70 |

| 5.2.2. Overall Control with Active Resonance Damper             | 78  |

|-----------------------------------------------------------------|-----|

| Chapter 6 : Simulation                                          | 80  |

| 6.1. Passive Resonance Damper Control Simulation                | 80  |

| 6.1.1. PSIM Set-up (Passive Resonance Damping)                  | 81  |

| 6.1.2. Waveforms Observation (Passive Resonance Damping)        | 83  |

| 6.1.2.1. Waveforms With and Without Power Decoupling Control    | 83  |

| 6.1.2.2. Leakage Current Waveform with Power Decoupling Control | 85  |

| 6.1.3. Efficiency of the System (Passive Resonance Damping)     | 86  |

| 6.2. Active Resonance Damper Control Simulation                 | 89  |

| 6.2.1. PSIM Set-up (Active Resonance Damping)                   | 89  |

| 6.2.2. Waveforms Observation (Active Resonance Damping)         | 91  |

| 6.2.2.1. Waveforms With and Without Power Decoupling Control    | 91  |

| 6.2.2.2. Ground Leaking Current Waveform                        | 93  |

| 6.2.2.3. Effect of Notch Filter                                 | 93  |

| 6.2.2.4. Effect of Grid-Side Inductance Variation               | 95  |

| 6.3. Efficiency of the System (Active Resonance Damping)        | 97  |

| Chapter 7 : Conclusion & Future Work                            | 99  |

| 7.1. Conclusion                                                 | 99  |

| 7.2. Future Work                                                | 100 |

| REFERENCES                                                      | 101 |

| APPENDIX110                                          |

|------------------------------------------------------|

| A1: Components                                       |

| A2: Waveforms                                        |

| A2.1. Passive Resonance Damping Controller Waveforms |

| A2.1.1. Duty Cycles                                  |

| A2.1.2. Currents                                     |

| A2.1.2.1. AC currents                                |

| A2.1.2.2. DC Current                                 |

| A2.1.3. Voltages                                     |

| A2.2. Active Resonance Damping Controller Waveforms  |

| A2.2.1. Duty cycles                                  |

| A2.2.2. Currents:                                    |

| A2.2.2.1. AC currents                                |

| A2.2.2.2. DC currents                                |

| A2.2.3. Voltages                                     |

# **List of Figures**

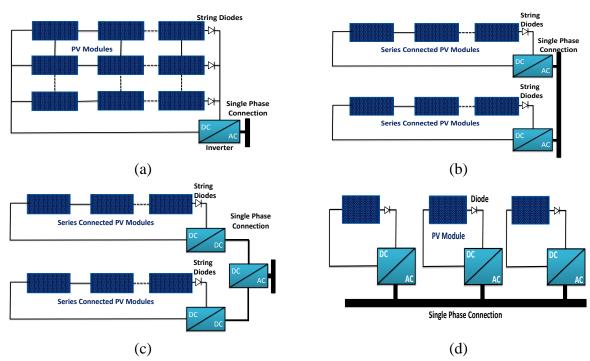

| Figure 1.1: Structural comparison between conventional inverter configuration and microinverter                 |

|-----------------------------------------------------------------------------------------------------------------|

| configuration in grid-connected PV systems: (a) centralized configuration, (b) string configuration, (c)        |

| multi-string configuration and (d) microinverter configuration                                                  |

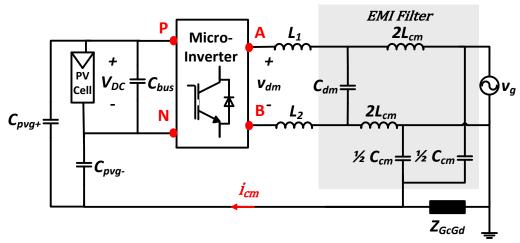

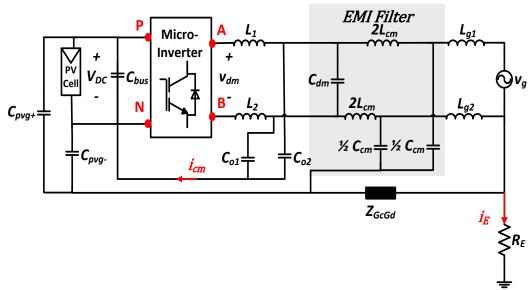

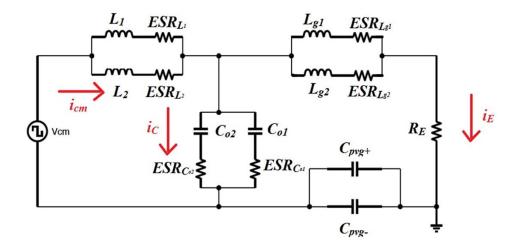

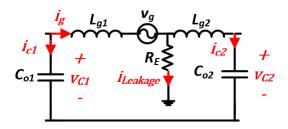

| Figure 2.1: Transformerless PV microinverter general circuit configuration with parasitic elements              |

| representation                                                                                                  |

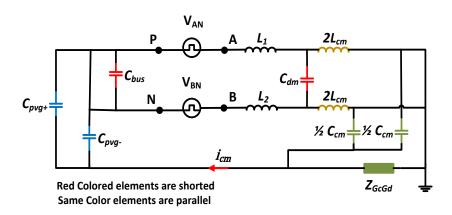

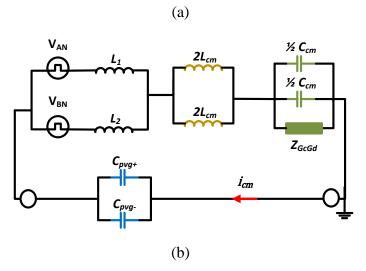

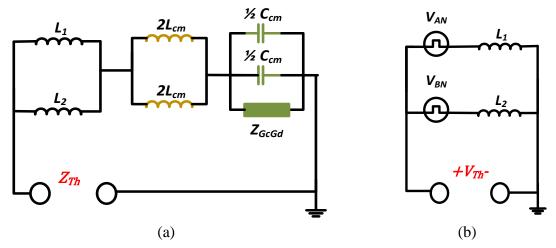

| Figure 2.2: Microinverter high frequency CM model: (a) steps to obtain the high frequency CM circuit and        |

| (b) the high frequency CM equivalent circuit                                                                    |

| Figure 2.3: Microinverter modified CM equivalent circuit: (a) analysis to obtain $Z_{Th}$ and (b) analysis to   |

| obtain V <sub>Th</sub> 9                                                                                        |

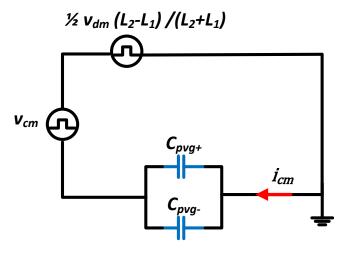

| Figure 2.4: CM noise simplified circuit model suggested by [35]                                                 |

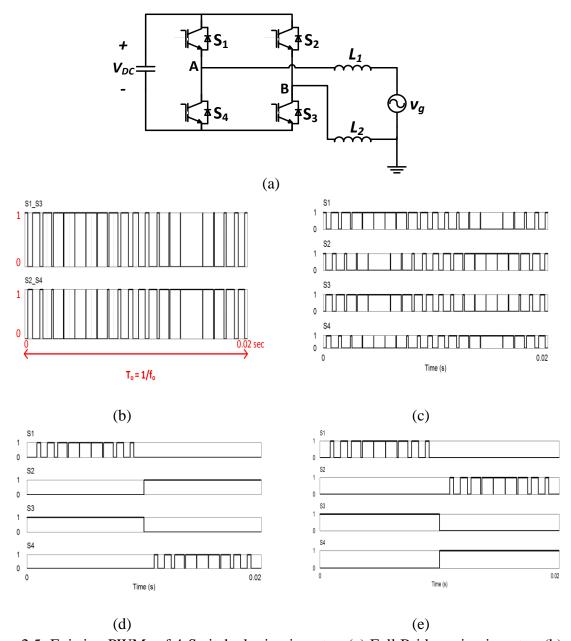

| Figure 2.5: Existing PWMs of 4-Switched microinverter: (a) Full Bridge microinverter, (b) Bipolar               |

| modulation [39], (c) Standard Unipolar modulation, (d) Unipolar II modulation and (e) Unipolar III              |

| modulation [40]                                                                                                 |

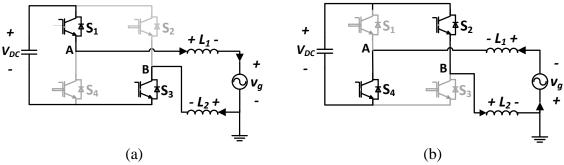

| Figure 2.6: Bipolar PWM operation modes [39]: (a) During the positive output, (b) during the negative           |

| output                                                                                                          |

| Figure 2.7: Standard Unipolar modulation operation modes [39]: (a) and (b) equivalent circuits in the           |

| positive half cycle, (c) and (d) in the negative half cycles                                                    |

| Figure 2.8: H5 microinverter: (a) configuration and (b) PWM scheme [36], [45], [46], [47]17                     |

| Figure 2.9: H6 microinverter (balanced losses): (a) configuration and (b) the PWM scheme [51]18                 |

| Figure 2.10: H6 microinverter operation modes [51]: (a) and (b) equivalent circuits in the positive half cycle, |

| (c) and (d) in the negative half cycles                                                                         |

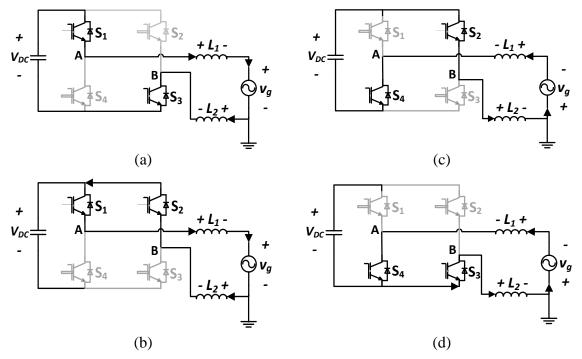

| Figure 2.11: Two possible topologies of H6 microinverter with reduced conduction losses [52]                    |

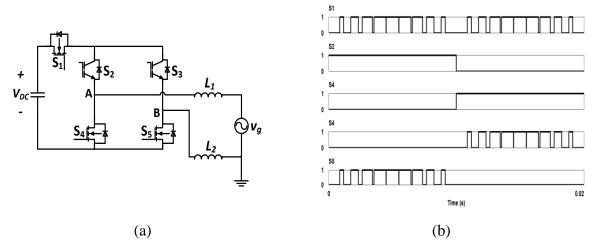

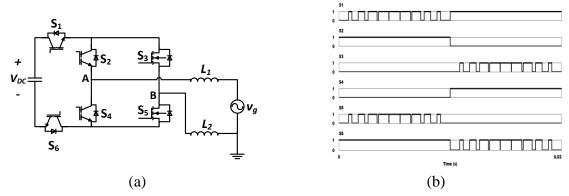

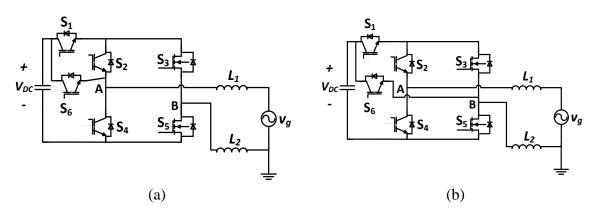

| Figure 2.12: Existing DC-based Neutral Point Clamped (NPC) Microinverters: (a) Passive Neutral Point            |

| Clamp (PNPC) Microinverter [57], [58] and (b) its PWM, (c) Active Neutral Point Clamp (ANPC)                    |

| Microinverter and (d) its PWM [55], [58]                                                                        |

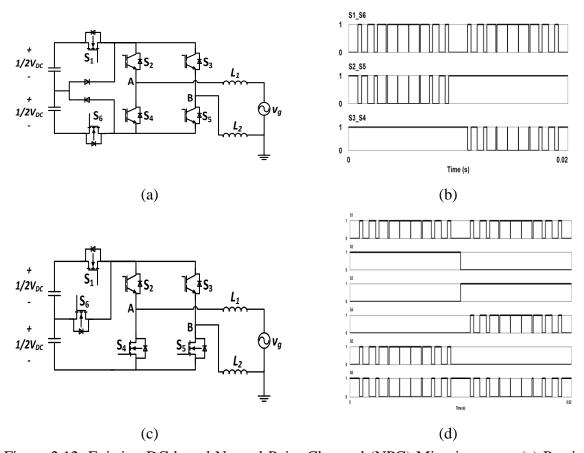

| Figure 2.13: H6 Passive NPC (PNPC) operation modes [57], [58]: (a) and (b) equivalent circuits in the                  |

|------------------------------------------------------------------------------------------------------------------------|

| positive half cycle, (c) and (d) in the negative half cycles                                                           |

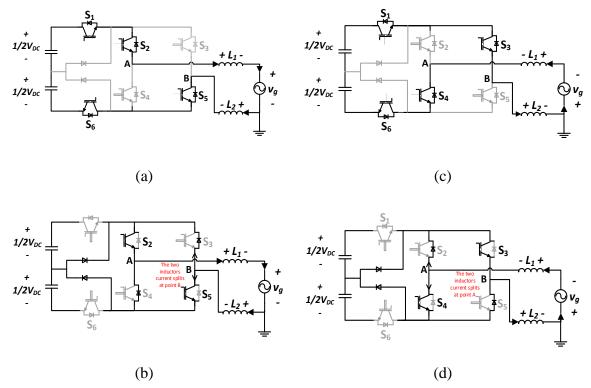

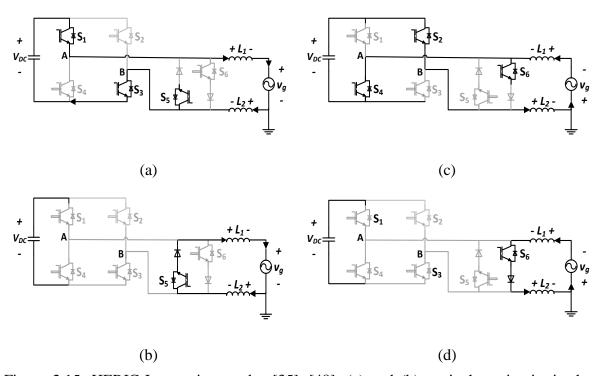

| Figure 2.14: Existing HERIC topologies: (a) HERIC-I [35],[36],[47], (b) HERIC-II [36], (c) HERIC-                      |

| III [52], (d) HERIC-IV [61] and (e) HERIC-V [60]                                                                       |

| Figure 2.15: HERIC-I operation modes [35], [48]: (a) and (b) equivalent circuits in the positive half cycle,           |

| (c) and (d) in the negative half cycles                                                                                |

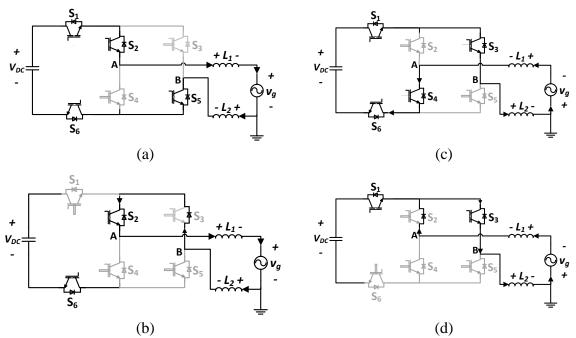

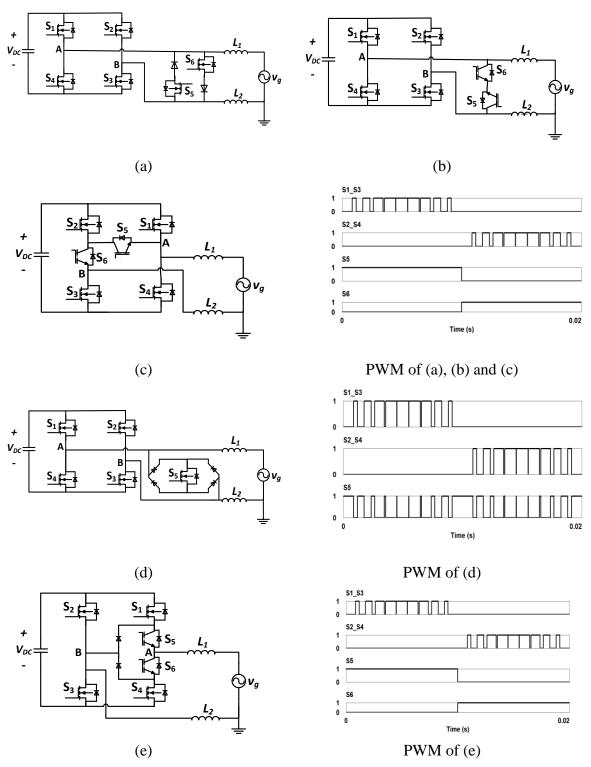

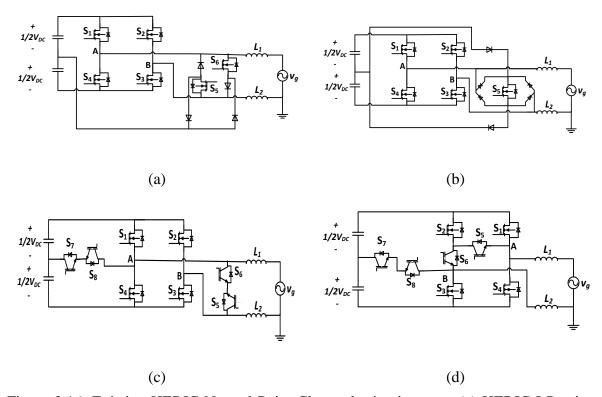

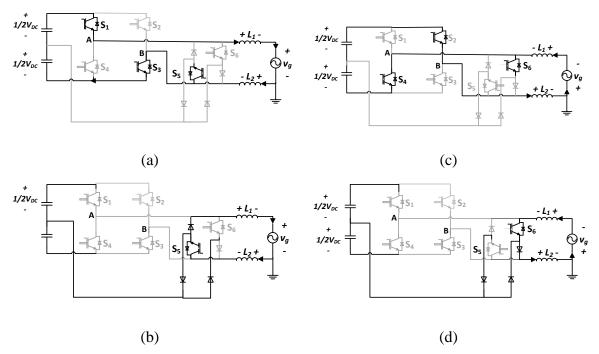

| Figure 2.16: Existing HERIC Neutral Point Clamped microinverters (a) HERIC-I Passive NPC [25], (b)                     |

| HERIC-IV Passive NPC [25], [53] (c) HERIC-II Active NPC , and (d) HERIC-III Active NPC27                               |

| Figure 2.17: HERIC-I Passive NPC microinverter operation modes [25]: (a) and (b) equivalent circuits in                |

| the positive half cycle, (c) and (d) in the negative half cycles                                                       |

| Figure 2.18: Transformerless PV microinverter configuration with parasitic elements representation and the             |

| CM filter [63], [64]                                                                                                   |

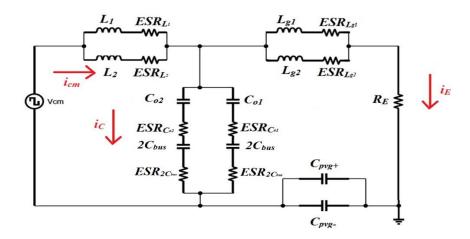

| Figure 2.19: CM equivalent circuit of the microinverter with the CM filter (midpoint of the two output split           |

| capacitors is connected to the negative DC bus)                                                                        |

| Figure 2.20: CM equivalent circuit of the microinverter with the CM filter (midpoint of the two split                  |

| capacitors is connected to the midpoint of the two series DC-link capacitors ( $C_{bus}$ =2 $C_{bus}$ +2 $C_{bus}$ )32 |

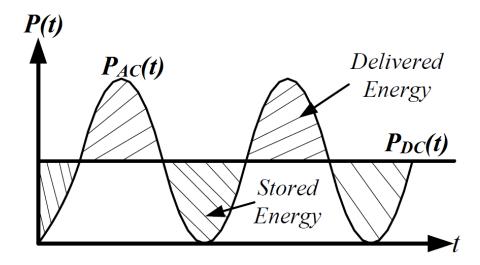

| Figure 2.21: Instantaneous power in the system and the total power processed by the decoupling capacitor34             |

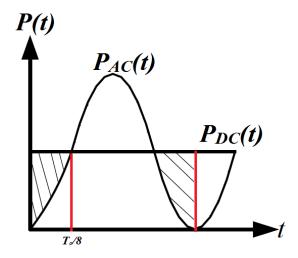

| Figure 2.22: AC-side power (output power) and DC-side power (PV side power) waveforms                                  |

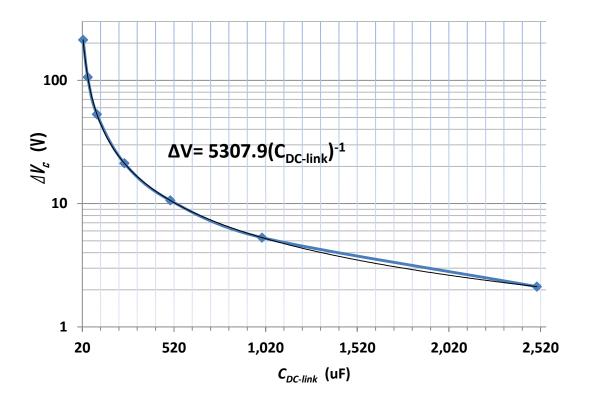

| Figure 2.23: The DC-link voltage ripple vs. the DC link capacitance value for the 600W H-Bridge                        |

| microinverter (The y-axis is in logarithmic scale)                                                                     |

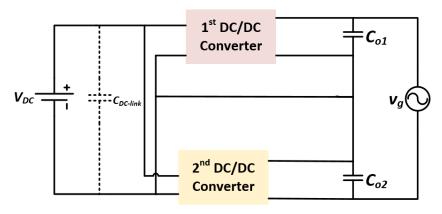

| Figure 2.24: General differential microinverter configuration                                                          |

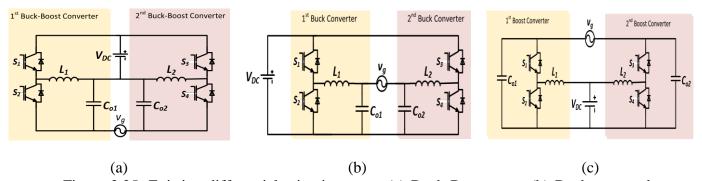

| Figure 2.25: Existing differential microinverters: (a) Buck-Boost type, (b) Buck type and (c) Boost type 38            |

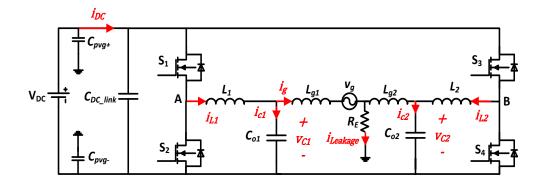

| Figure 2.26: Differential Buck microinverter (with grid parasitic elements and the PV terminals stray                  |

| capacitances)                                                                                                          |

| Figure 2.27: Microinverter point of common coupling with the grid loop                                                 |

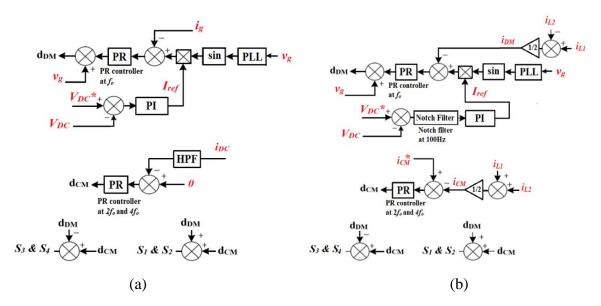

| Figure 2.28: Existing transistorless power decoupling control schemes: (a) autonomous control scheme [77],             |

| and (b) non-autonomous control scheme [63]                                                                             |

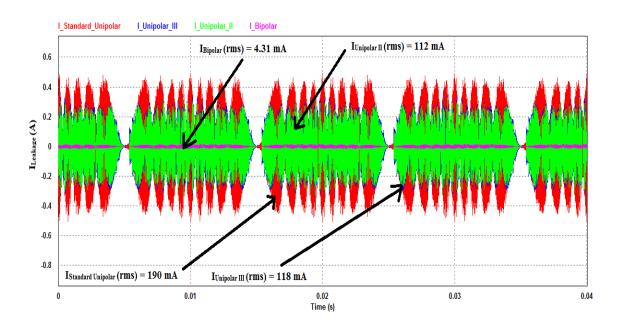

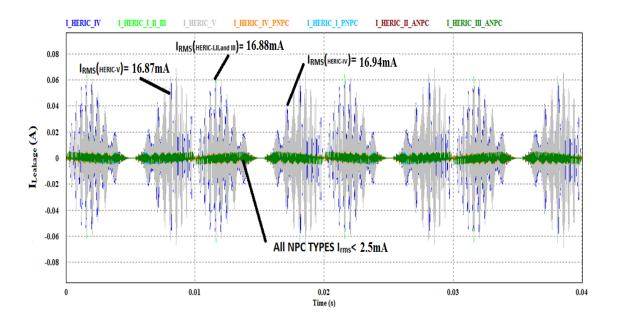

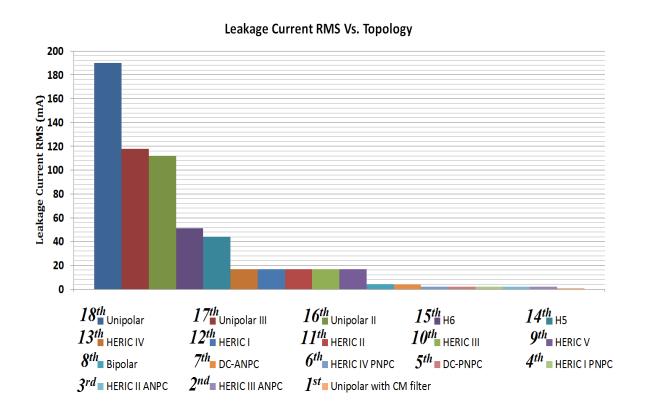

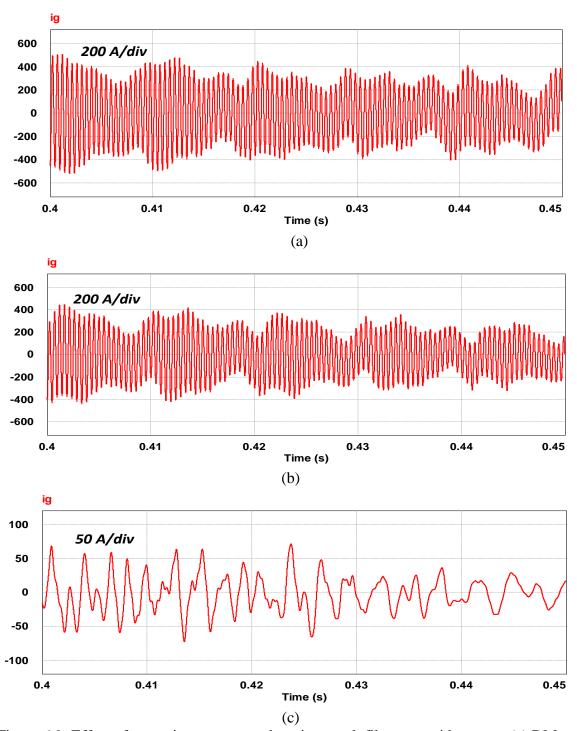

| Figure 3.1: Existing 4-Switch microinverters leakage current with different PWMs in PSIM                    | 47 |

|-------------------------------------------------------------------------------------------------------------|----|

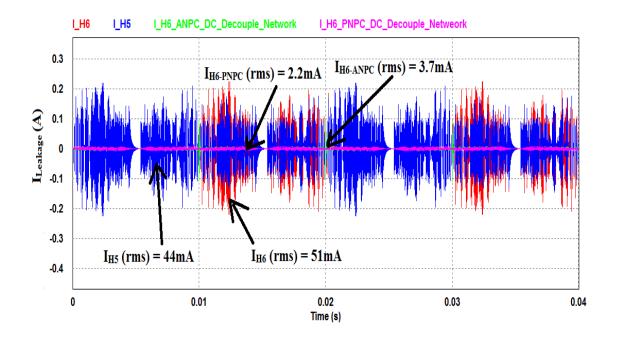

| Figure 3.2: Leakage current generated by different DC-decoupling network microinverters                     | 48 |

| Figure 3.3: Leakage current generated by different HERIC (AC decoupling network) microinverters             | 49 |

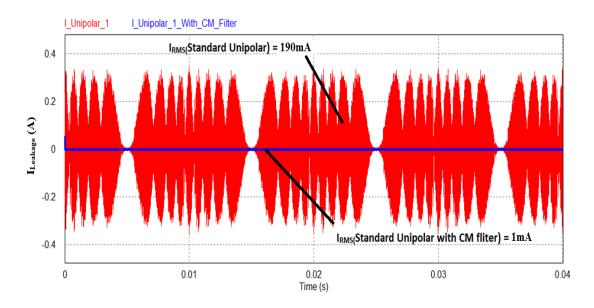

| Figure 3.4: Leakage current with LC CM passive filter compared to the conventional H-bridge microinverte    | er |

| with standard unipolar modulation                                                                           | 50 |

| Figure 3.5: Ranking of topologies based on their leakage current RMS values                                 | 51 |

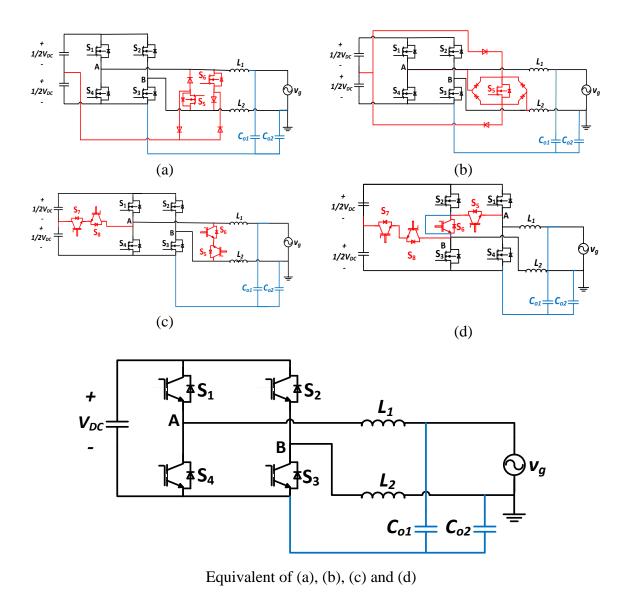

| Figure 3.6: Power decoupling output capacitors addition to the HERIC NPC types and its equivalent           | nt |

| configuration                                                                                               | 53 |

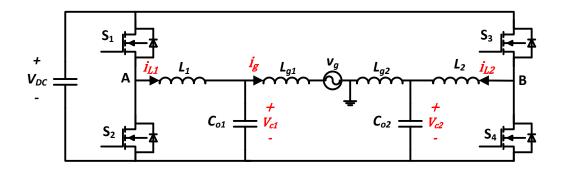

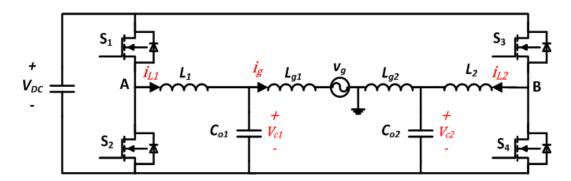

| Figure 4.1. The differential buck configuration with LCL filter                                             | 55 |

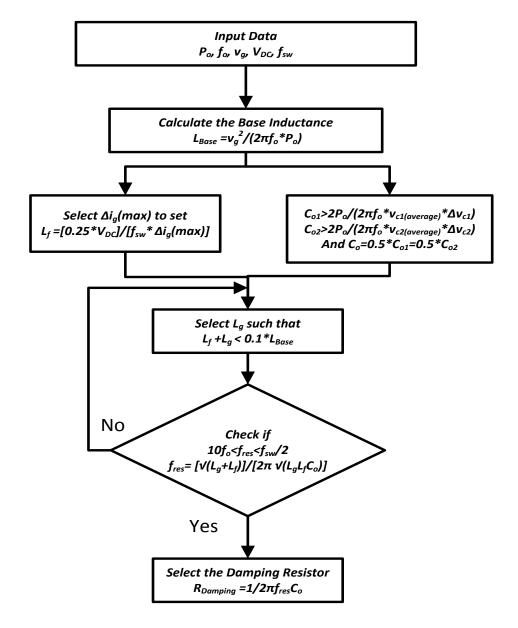

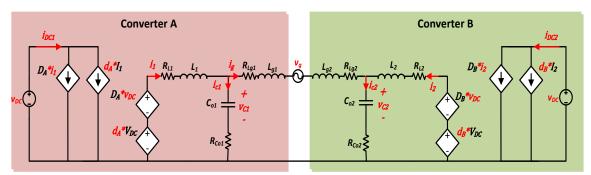

| Figure 5.1: Differential Buck LCL filter equivalent circuit in the DM: (a) detailed DM model and (b)        | )  |

| simplified model                                                                                            | 57 |

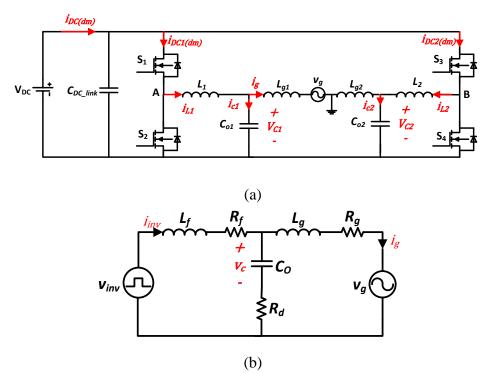

| Figure 5.2: Flowchart for LCL filter with Differential buck parameters selection                            | 59 |

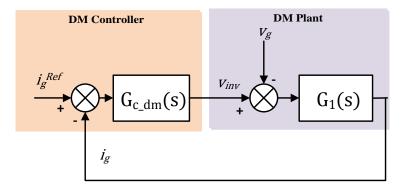

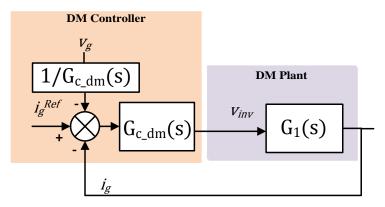

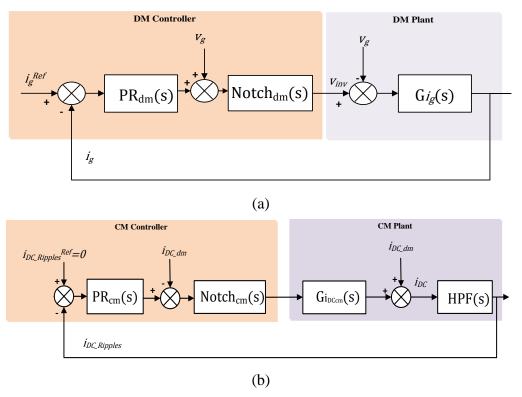

| Figure 5.3: DM controller and the microinverter DM plant                                                    | 61 |

| Figure 5.4: Modified DM control                                                                             | 63 |

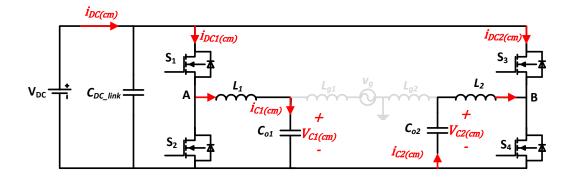

| Figure 5.5: CM equivalent circuit of the differential buck microinverter                                    | 65 |

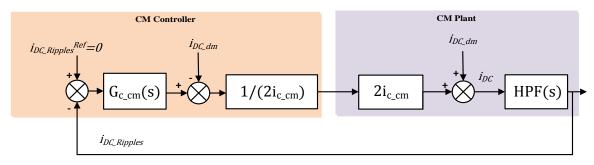

| Figure 5.6: CM controller and the CM plant                                                                  | 67 |

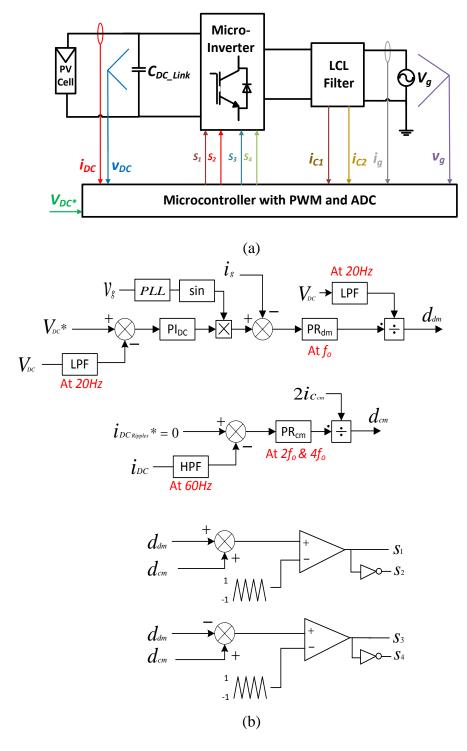

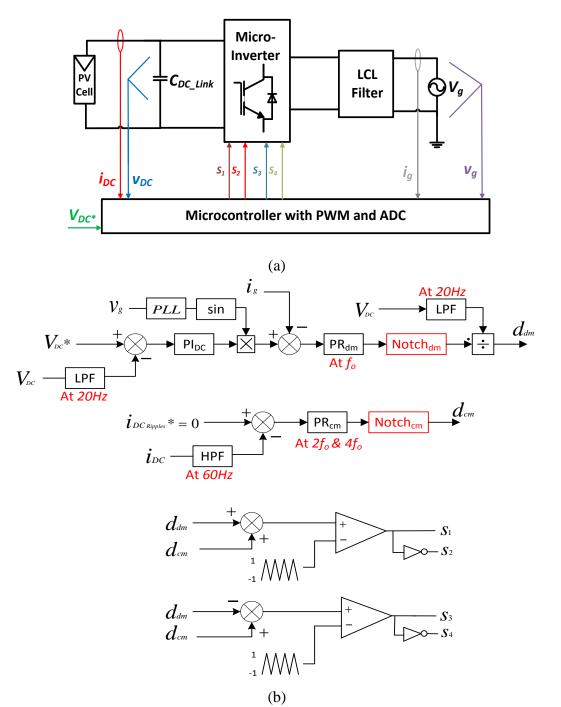

| Figure 5.7: Passive resonance damping overall control structure differential buck microinverter: (a) Sensor | rs |

| and microinverter block diagram and (b) detailed controller structure                                       | 69 |

| Figure 5.8: Grid connected differential buck small signal model (Red color indicates a perturb value)       | 71 |

| Figure 5.9 Active damper controller detailed models: (a) DM controller and (b) CM controller                | 76 |

| Figure 5.10: Active resonance damping control structure with differential buck microinverter: (a) Sensor    | rs |

| and microinverter block diagram and (b) detailed controller structure                                       | 79 |

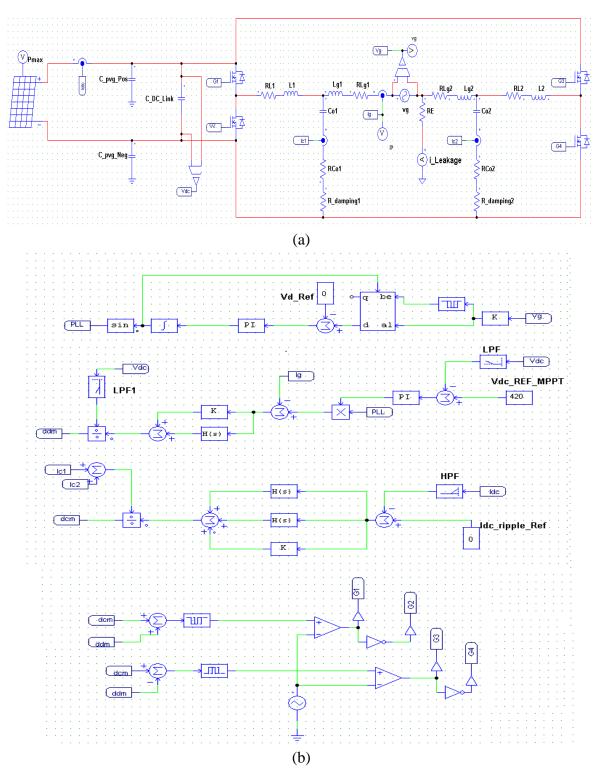

| Figure 6.1: System set-up in PSIM (Passive damper control): (a) circuit set-up and (b) controller structure | 82 |

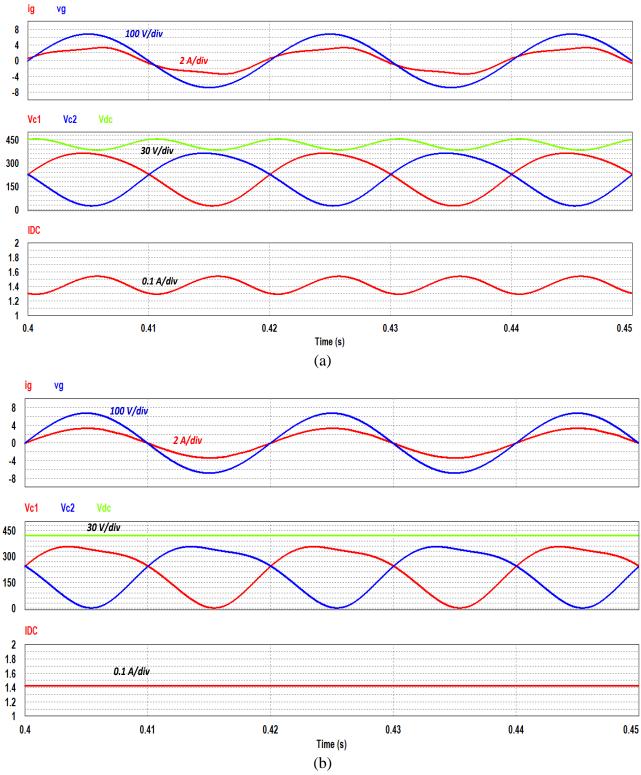

| Figure 6.2: Essential waveforms (Passive damper control): (a) without power decoupling control and (b)      | )) |

| with power decoupling control                                                                               | 84 |

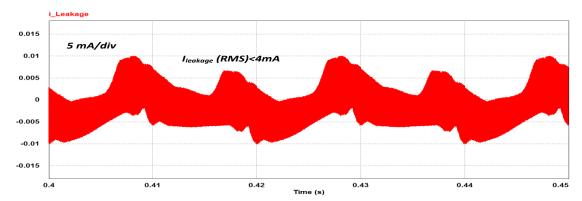

| Figure 6.3: Ground leaking current with power decoupling control (Passive damper control)                   | 86 |

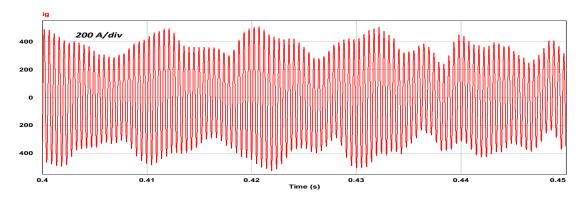

| Figure 6.4: Effect of removing the damping resistors on the grid current                                    | 86 |

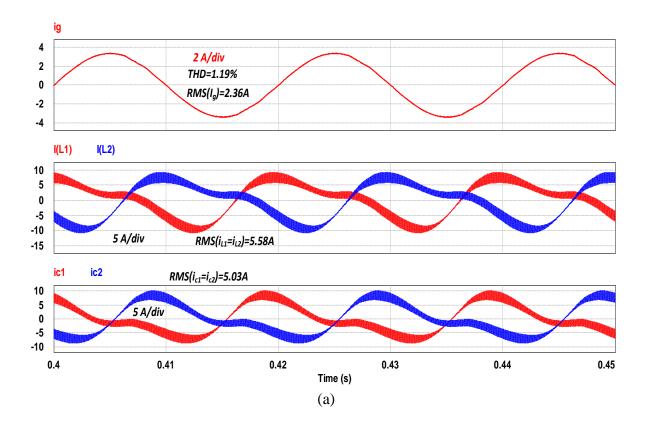

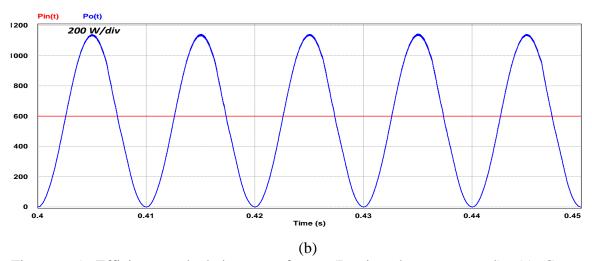

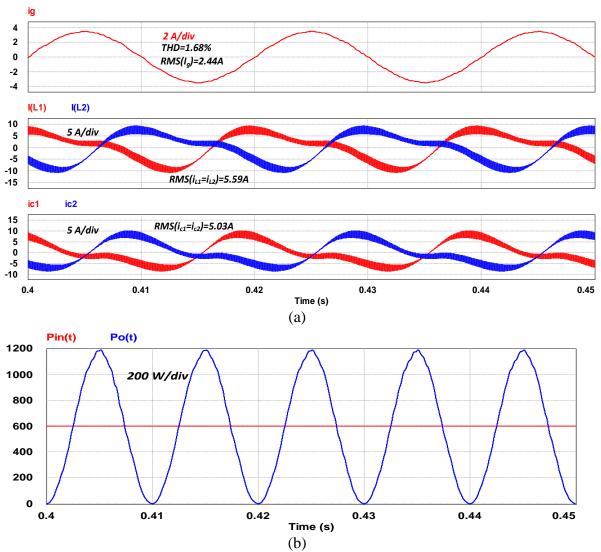

| Figure 6.5: Efficiency calculation waveforms (Passive damper control): (a) Currents waveforms and (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| instantaneous output power waveform compared to the instantaneous input power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

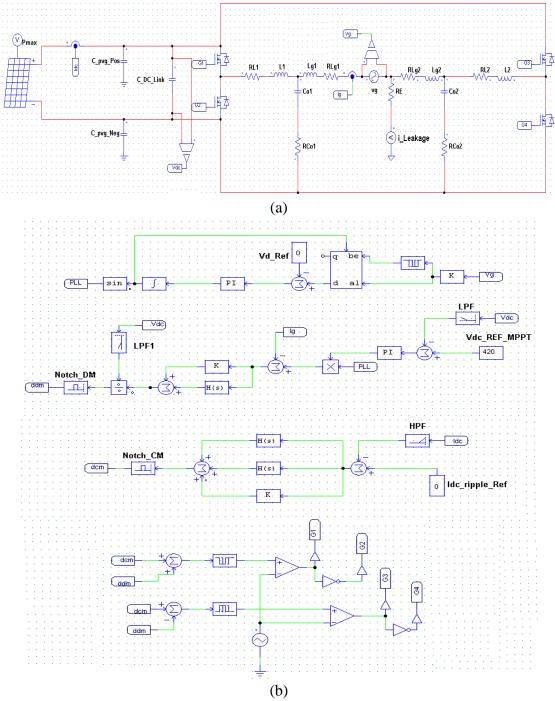

| Figure 6.6: System set-up in PSIM (Active Damper Control): (a) Circuit set-up and (b) controller structure. 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

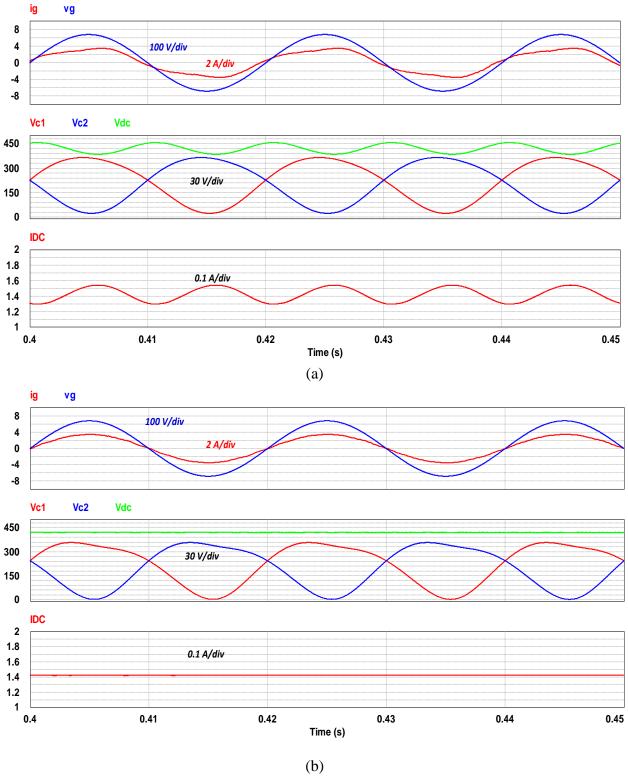

| Figure 6.7: Essential waveforms (Active damper control): (a) without power decoupling control and (b) with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| power decoupling control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

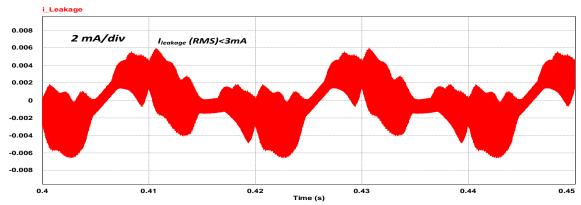

| Figure 6.8: Ground leaking current with power decoupling control (Active damper control)93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 6.9: Effect of removing resonance damping notch filters on grid current: (a) DM and CM notch filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| removal, (b) DM notch filter removal and (c) CM notch filter removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

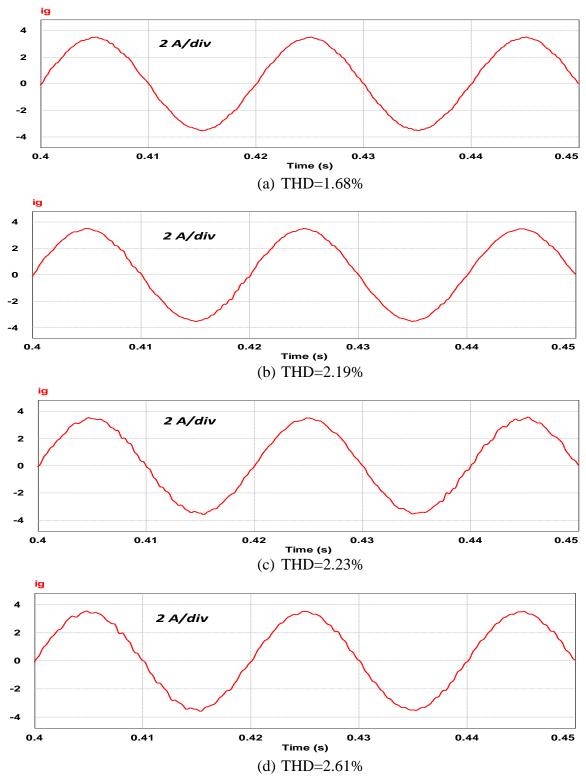

| Figure 6.10: Effect of grid-side inductance increase on the grid current: (a) 0% increase, (b) 25% increase,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (c) 50% increase and (d) 100% increase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 6.11: Efficiency calculation waveforms (Active damper control): (a) Currents waveforms and (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| instantaneous output power waveform compared to the input power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure A1.1: Differential buck microinverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

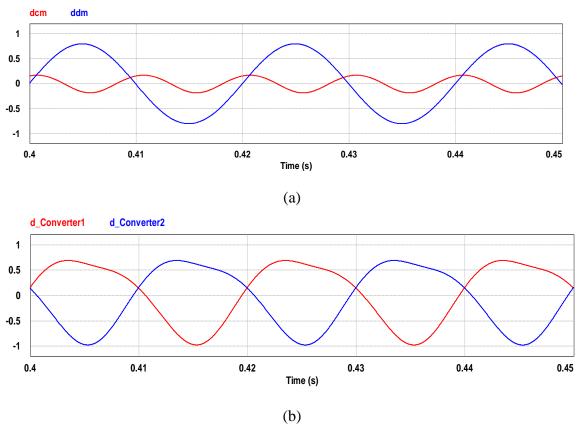

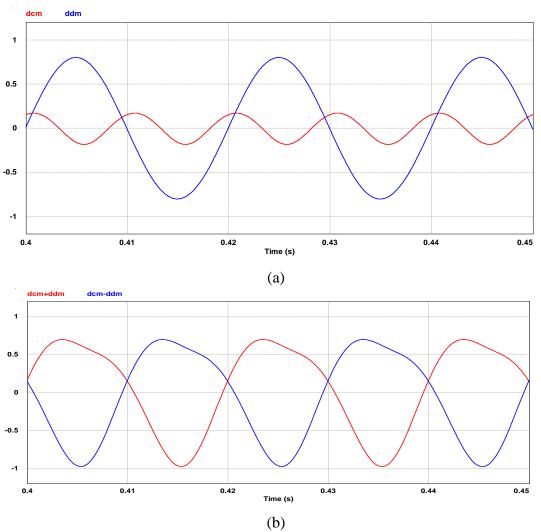

| Figure A2.2: Duty cycles (Passive): (a) DM and CM duty cycles, and (b) each microinverter leg duty cycle112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

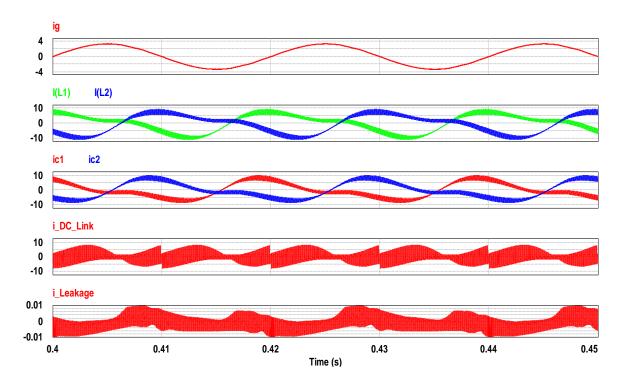

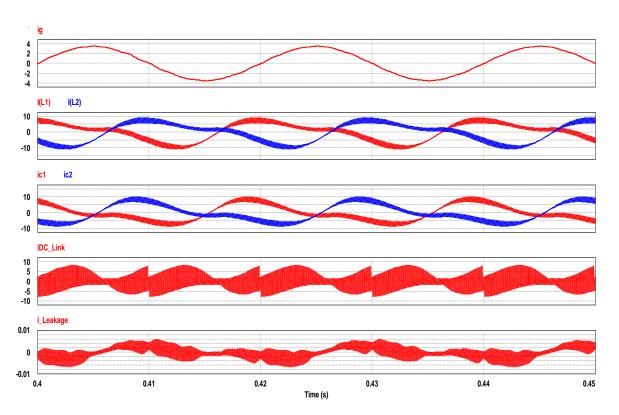

| Figure A2.3: AC Current waveforms (Passive): $i_g$ (2 A/div), $i_{Ll}$ (5 A/div), $i_{L2}$ (5 A/div), $i_{Cl}$ (6 A/div), $i_{Cl}$ (7 A/div), $i_{Cl}$ (8 A/div), $i_{Cl}$ (9 A/div), $i_$ |

| A/div), $i_{DC\_Link}$ (5 A/div) and $i_{Leakage}$ (2 mA/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

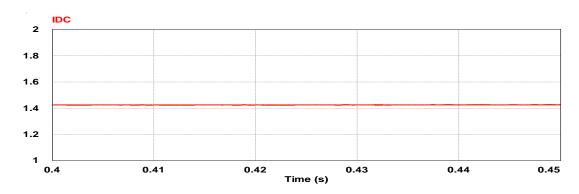

| Figure A2.4: DC supply current (Passive) (0.2 A/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

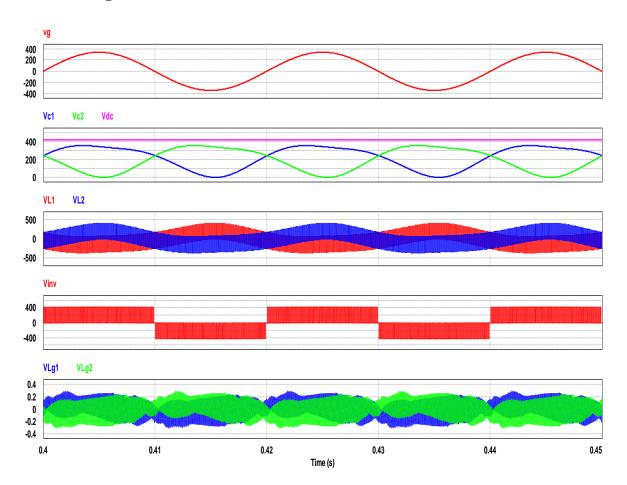

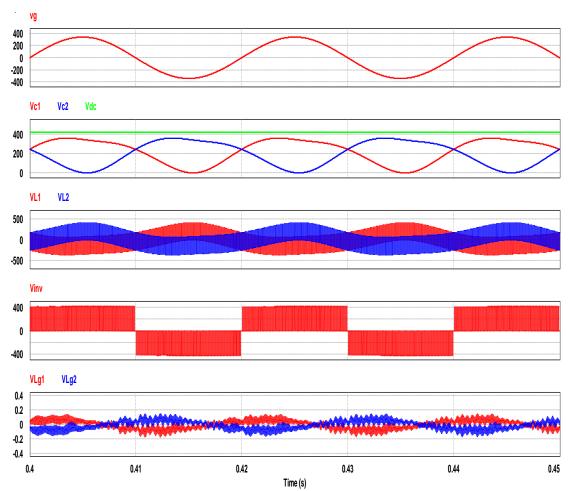

| Figure A2.5: Voltage waveforms (Passive): $v_g$ (200 V/div), $v_{Cl}$ (100 V/div), $v_{C2}$ (100 V/div), $V_{DC}$ (100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V/div), $v_{LI}$ (500 A/div), $v_{L2}$ (500 V/div) and $v_{inv}$ (200 V/div), $v_{LgI}$ (0.2 V/div) and $v_{Lg2}$ (0.2 V/div)114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure A2.6: Duty cycles (Active): (a) DM and CM duty cycles, and (b) each microinverter leg duty cycle 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure A2.7: AC Current waveforms (Active): $i_g$ (2 A/div), $i_{L1}$ (5 A/div), $i_{L2}$ (5 A/div), $i_{C1}$ (5 A/div), $i_{C2}$ (5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A/div), $i_{DC\_Link}$ (5 A/div) and $i_{Leakage}$ (2 mA/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure A2.8: DC supply current (Active) (0.2 A/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure A2.9: Voltage waveforms (Active): $v_g$ (200 V/div), $v_{CI}$ (200 V/div), $v_{C2}$ (200 V/div), $V_{DC}$ (200 V/div),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $v_{LI}$ (500 A/div), $v_{L2}$ (500 V/div) and $v_{inv}$ (200 V/div), $v_{LeI}$ (0.2 V/div) and $v_{Le2}$ (0.2 V/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# **List of Tables**

| Table 2.1: The two output capacitors voltage limitation with different configurations |    |

|---------------------------------------------------------------------------------------|----|

| Table 3.1 Parameters used in the study of the leakage current                         | 46 |

| Table 4.1: Parameters used in the modeling and design stage                           | 54 |

| Table 5.1: Differential Buck with LCL equivalent parameters in the DM                 | 57 |

| Table 5.2: Selected LCL filter Parameters                                             | 60 |

| Table 5.3: PR compensator parameters                                                  | 64 |

| Table 5.4: CM controller gains                                                        | 68 |

| Table 5.5: Assumptions in the small signal analysis                                   | 72 |

| Table 5.6: Active damper components                                                   | 77 |

| Table 5.7: Controller gains                                                           | 77 |

| Table 6.1 component values used in PSIM simulation (Passive Damper Control)           | 81 |

| Table 6.2: Currents RMS values and power losses (Passive damper control)              | 87 |

| Table 6.3: component values used in PSIM simulation (Active Damper Control)           | 89 |

| Table 6.4: Currents RMS values and power losses (Active damper control)               | 97 |

# **Chapter 1: Introduction**

#### 1.1. Background

The rapid increase in the energy demand is coupled with the rapid exhaustion of the limited fossil fuel sources. This fact increased the global requirement for clean energy sources and efficient and reliable harnessing technologies [1]-[5]. Unlike fossil fuel based systems, technologies involved in the utilization of renewable energy resources such as solar energy, wind energy and biomass energy are environmentally clean and this is the reason why these sources are more significant in this century. For instance, sun's energy is inexhaustible, effective and environmentally friendly [6]-[10]. Also, the energy generated from photovoltaic (PV) modules is one of the elegant examples of harnessing solar energy, as it is clean, pollutant-free and modular [11]. Beside, PV modules are noiseless, require low maintenance and have simple operation [12]. Since most power systems and loads are AC, PV module's DC output power is unsuitable for them and many power conversion stages must be added. Traditionally, PV DC output power is converted to an AC-side power through a single central inverter (Figure 1.1 (a)) or by the other different conventional configurations as in Figure 1.1 (b) and (c). Also, to assure that the system is extracting the maximum power from the PV panel, a DC/DC converter is used with maximum power point tracking (MPPT) algorithm and it is connected prior to the inverter.

However, the traditional methodology used in grid-connected PV systems is challenged by a new methodology. Specifically, multiple small inverters are deployed

with each PV module and their output is connected in parallel with the utility grid (Figure 1.1 (d)). These small inverters are called Microinverters. According to [13]-[15], microinverter-based PV systems improve energy harvest and system efficiency. In addition, microinverter-based PV system reduces installation cost, boosts flexible future expandability option and increases system modularity [13]-[15]. Microinverter configuration is crucial to Gulf Cooperation Council (GCC) region countries because microinverter provide a flexible future expandability option instead of derating or overrating the central or the string inverter in case of PV system expansion or expected expansion. Figure 1.1 shows a structural comparison between the microinverter configuration and the conventional configurations in PV systems. Note that, ratings of

Figure 1.1: Structural comparison between conventional inverter configuration and microinverter configuration in grid-connected PV systems: (a) centralized configuration, (b) string configuration, (c) multi-string configuration and (d) microinverter configuration

microinverters are related to the commercially available PV modules which are between 200W and 700W [16].

Grid-connected microinverters are classified as transformer or transformerless type based on the existence of galvanic isolation. The galvanic isolation is realized practically with a transformer. In addition to isolation, these transformers can be utilized as voltage boosters. Moreover, the transformer in the microinverter is either placed in the AC side with line frequency operation or in the DC side with high frequency operation. Unfortunately, line frequency transformers are impractical because line frequency transformers are bulky. Similarly, the high frequency transformers also introduce extra losses. According to [17], removing the transformer from the inverter or microinverter achieves 1% to 2% higher efficiency, improves the power density and reduces the cost [18]-[20]. Thus, microinverter developers are recently concentrating on transformerless designs.

However, this global movement toward transformerless designs raised a safety flag regarding the loss of galvanic isolation and the amount of the circulating leakage current [21]. This leakage current is caused by the existence of the parasitic capacitance between the PV terminals and the ground. In addition, leakage current circulation causes power losses, current harmonics and electromagnetic interference [21], [22]. Therefore, the suppression of this leakage current improves the reliability of the system [23]. Recently, new requirements were added to the German PV system grid connection standard -Verband Der Elektrotechnik (VDE) - about the maximum leakage current magnitude and its sudden variation [24]; if the leakage current is over 300mA RMS or

the sudden variation reaches 30mA RMS the inverter is automatically disconnected from the grid irrespective of the power conversion level [25].